Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

**ISSUE 3**

ENHANCED TT1™ SWITCH FABRIC

## PM9311/2/3/5

# **Enhanced TT1 Chip Set**

## **Enhanced TT1 Switch Fabric**

## **Datasheet**

Issue 3: August 2001

Data Sheet

PMC-2000164

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

This document is the proprietary and confidential information of PMC-Sierra Inc. Access to this information does not transfer or grant any right or license to use this intellectual property. PMC-Sierra will grant such rights only under a separate written license agreement.

Any product, process or technology described in this document is subject to intellectual property rights reserved by PMC-Sierra, Inc.and are not licensed hereunder. Nothing contained herein shall be construed as conferring by implication, estoppel or otherwise any license or right under any patent or trademark of PMC-Sierra, Inc.or any third party. Except as expressly provided for herein, nothing contained herein shall be construed as conferring any license or right under any PMC-Sierra, Inc.copyright.

Each individual document published by PMC-Sierra, Inc. may contain additional or other proprietary notices and/or copyright information relating to that individual document.

THE DOCUMENT MAY CONTAIN TECHNICAL INACCURACIES OR TYPOGRAPHICAL ERRORS. CHANGES ARE REGULARLY MADE TO THE INFORMATION CONTAINED IN THE DOCUMENTS. CHANGES MAY OR MAY NOT BE INCLUDED IN FUTURE EDITIONS OF THE DOCUMENT. PMC-SIERRA, INC.OR ITS SUPPLIERS MAY MAKE IMPROVEMENTS AND/OR CHANGES IN THE PRODUCTS(S), PROCESS(ES), TECHNOLOGY, DESCRIPTION(S), AND/OR PROGRAM(S) DESCRIBED IN THE DOCUMENT AT ANY TIME.

THE DOCUMENT IS PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTY OR MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT.

ETT1, Enhanced TT1, TT1, and LCS are trademarks of PMC-Sierra, Inc.

© 2000 PMC-Sierra, Inc. 8555 Baxter Place Burnaby BC Canada V5A 4V7 Phone: (604) 415-6000 FAX: (604) 415-6200

Data Sheet

PMC-2000164

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

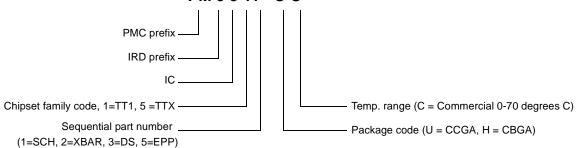

## **Device Part Numbers**

This document contains information on the ETT1<sup>™</sup> Chip Set, available from PMC-Sierra, Inc. The following devices comprise the ETT1 Chip Set:

| Device Name             | PMC Part Number |

|-------------------------|-----------------|

| Scheduler               | PM9311-UC       |

| Crossbar                | PM9312-UC       |

| Dataslice               | PM9313-HC       |

| Enhanced Port Processor | PM9315-HC       |

Data Sheet

PMC-2000164

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

## **Revision History**

| Issue Number | Issue Date  | Details Of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | March 2000  | Creation of document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2            | July 2000   | Added HSTL Power Dissipation values, corrected programming<br>constraints for EPP, added OOB, JTAG and PLL blocks to device<br>dataflow diagrams, added heat sink information to Characteristics<br>section, corrected EPP register section, corrected Frame Format<br>tables, added correct bit definition for EPP Interrupt register,<br>corrected diagram in Appendix C, added send and receive<br>procedure for control packets, added ESOBLCP register<br>explanation, corrected conditions in Table 57, corrected Scheduler<br>Refresh Procedure, added new drawing for Crossbar data flow,<br>corrected token explanation, corrected Figures 36 and 37,<br>corrected spelling and formatting errors throughout document.                                                                                                                                                                                                                                                                                  |

| 3            | August 2001 | Removed bit 17 from Scheduler Status Register, updated BP_FIFO<br>information in Scheduler Control and Reset Register, corrected<br>bottom view drawings for Scheduler and Crossbar, corrected signal<br>description section in Scheduler and Crossbar for power pins,<br>corrected tper3, and tpl3 in AC Electrical, added memory address<br>information in EPP registers, corrected mechanical drawings,<br>updated state diagram in Scheduler, added information about<br>Scheduler PLL timing, updated initialization sequence for all chips,<br>corrected Dataslice Signal Description for ibpen0, added bit 14(13th<br>and 14th Dataslice enable) to EPP Control register, updated TDM<br>constraints, added Output TDM Queue Overflow to the EPP's<br>Interrupt register, updated EPP Output Backpressure /<br>Unbackpressure Threshold register, updated LCS2 link<br>synchronization in appendix, modified EPP Egress Control Packet<br>Data Format table, Modified ETT1 usage of LCS2 protocol section |

PMC-2000164

Data Sheet

| ISSUE 3 |

|---------|

|---------|

| 1 | Fun | ctiona | al Description                                    | 15   |

|---|-----|--------|---------------------------------------------------|------|

|   | 1.1 | Over   | view                                              | 15   |

|   |     | 1.1.1  | ETT1 Switch Core Features                         |      |

|   |     | 1.1.2  | The Switch Core Model                             |      |

|   |     | 1.1.3  | The LCS Protocol                                  |      |

|   |     | 1.1.4  | The OOB (Out-Of-Band) Bus                         | . 18 |

|   | 1.2 | Archi  | itecture and Features                             | 18   |

|   |     | 1.2.1  | ETT1 Switch Core                                  | . 18 |

|   |     | 1.2.2  | Basic Cell Flow                                   | . 19 |

|   |     | 1.2.3  | Prioritized Best-effort Service                   | . 21 |

|   |     | 1.2.4  | End-to-End Flow Control                           | . 22 |

|   |     | 1.2.5  | TDM Service                                       | . 22 |

|   |     | 1.2.6  | Subport Mode (2.5 Gbit/s Linecards)               | . 23 |

|   |     | 1.2.7  | LCS Control Packets                               | . 24 |

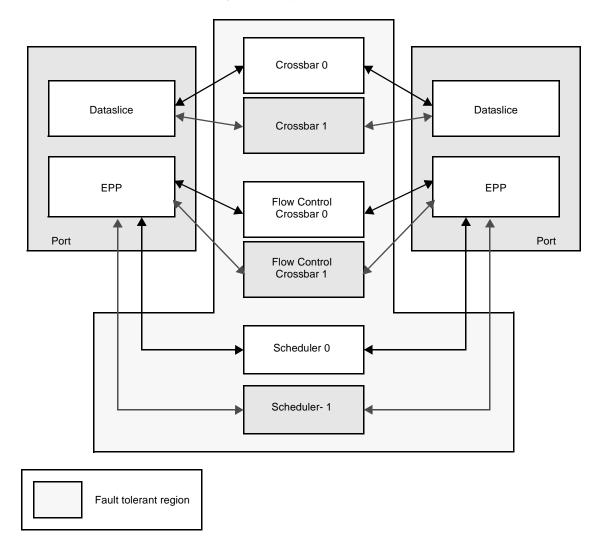

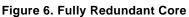

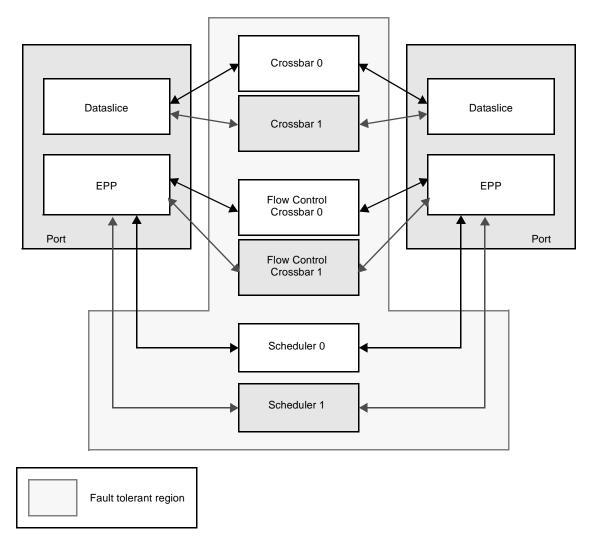

|   |     | 1.2.8  | Redundancy                                        | . 25 |

|   |     | 1.2.9  | System Configuration Options                      | . 28 |

|   | 1.3 | Priori | itized Best-Effort Queue Model                    | 30   |

|   |     | 1.3.1  | Unicast Traffic (OC-192).                         | . 31 |

|   |     | 1.3.2  | Multicast Traffic (OC-192)                        | . 31 |

|   |     | 1.3.3  | Unicast Traffic (Subport Mode)                    | . 33 |

|   |     | 1.3.4  | Multicast Traffic (subport mode)                  | . 46 |

|   |     | 1.3.5  | Combinations of OC-192c and Quad OC-48c Linecards | . 49 |

|   |     | 1.3.6  | Summary                                           | . 50 |

|   |     | 1.3.7  | The LCS Protocol                                  | . 51 |

|   | 1.4 | Expli  | cit Backpressure From oEPP to iEPP                | 52   |

|   |     | 1.4.1  | Flow Control Crossbar Synchronization             | . 54 |

|   | 1.5 | TDM    | Service                                           | 54   |

|   |     | 1.5.1  | TDM Queues                                        | . 54 |

|   |     | 1.5.2  | TDM Reservation Tables                            | . 55 |

|   |     | 1.5.3  | TDM Frame Timing                                  | . 59 |

|   |     | 1.5.4  | TDM Synchronization                               | . 59 |

|   |     | 1.5.5  | Configuring the TDM Service                       | . 62 |

|   |     | 1.5.6  | Changing the Source of the Suggested Sync         | . 63 |

|   | 1.6 | ETT1   | Usage of the LCS Protocol                         | 64   |

|   |     | 1.6.1  | LCS Protocol Prepend                              | . 64 |

|   |     | 1.6.2  | Use of Label and Type Fields                      | . 67 |

|   |     | 1.6.3  | Control Packets                                   | . 69 |

|   |     | 1.6.4  | Use of CRC Fields                                 | . 73 |

|   |     | 1.6.5  | LCS PHY Layer                                     | . 75 |

|   | 1.7 | The C  | Dut-of-Band (OOB) Bus Interface                   | 77   |

|   |     | 1.7.1  | The OOB Bus                                       | . 78 |

ISSUE 3

Data Sheet

PMC-2000164

| 1.8  | Initial | ization Procedure                              |

|------|---------|------------------------------------------------|

|      | 1.8.1   | Initial Power-on:                              |

|      | 1.8.2   | Port Board being added:                        |

|      | 1.8.3   | Scheduler Board being added:                   |

|      | 1.8.4   | Crossbar Board being added:                    |

| 1.9  | Fault   | Tolerance                                      |

|      | 1.9.1   | Fault Tolerance Model                          |

|      | 1.9.2   | Soft/Transient Errors                          |

|      | 1.9.3   | Flow Control Refresh Procedure                 |

|      | 1.9.4   | Scheduler Refresh Procedure                    |

|      | 1.9.5   | Refresh Schedulers After Modifying Registers   |

|      | 1.9.6   | Hard Errors                                    |

|      |         |                                                |

| 1.10 | ETT1    | Signals and Interconnections 102               |

|      | 1.10.1  | LVCMOS (C and O)                               |

|      | 1.10.2  | HSTL (H)                                       |

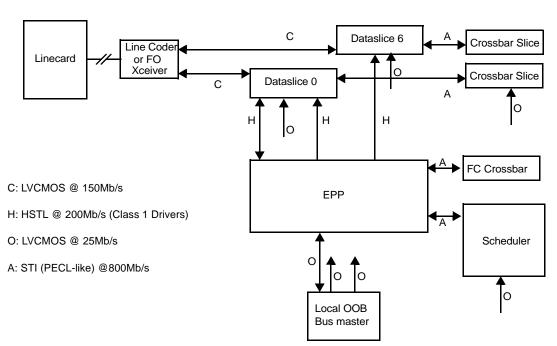

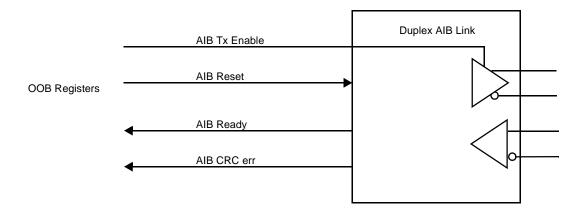

|      | 1.10.3  | AIB Links (A)                                  |

|      | 1.10.4  | Live Insertion                                 |

| 1 11 | Syste   | m Latencies                                    |

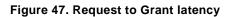

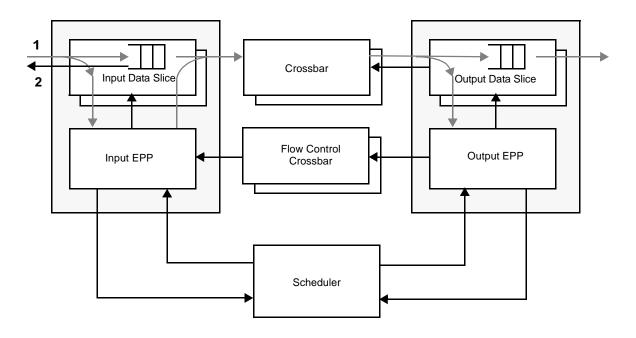

|      | 1.11.1  | LCS Request to Grant Minimum Latency           |

|      | 1.11.2  | LCS Grant to Linecard Cell Latency             |

|      | 1.11.2  | Cell latency Through an Empty System           |

|      | 1.11.4  | LCS Hole Request to Hole Grant Latency         |

|      |         |                                                |

| 1.12 | ETT1    | Diagnostics                                    |

|      | 1.12.1  | Device Tests                                   |

|      | 1.12.2  | AIB Link Tests                                 |

|      | 1.12.3  | Linecard to ETT1 Link Diagnostics              |

|      | 1.12.4  | ETT1 Internal Datapath Tests                   |

| Data | aslice  |                                                |

|      |         |                                                |

| 2.1  | Datas   | lice Blocks                                    |

|      | 2.1.1   | OOB Interface and Control/Status Registers 117 |

|      | 2.1.2   | Dataslice Cell Flow                            |

| 2.2  | 8B/10   | B Interface                                    |

| 2.3  | Datas   | lice Registers                                 |

| -    | 2.3.1   | Dataslice Summary                              |

|      | 2.3.2   | Dataslice Register Descriptions                |

|      | _       |                                                |

| 2.4  | Datas   | lice Signal Descriptions 136                   |

2

ISSUE 3

Data Sheet

PMC-2000164

| ENHANCED TT1™ SWITCH FABRIC |

|-----------------------------|

|-----------------------------|

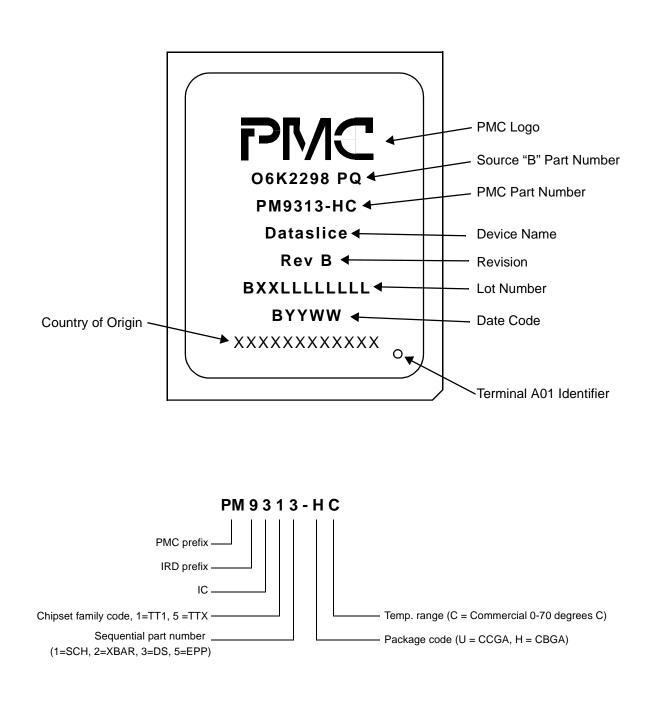

|   | 2.5 | Pinout and Package Information1422.5.1Pinout Tables1422.5.2Package Dimensions147                                                                                                                                                                |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _ |     | 2.5.3 Part Number                                                                                                                                                                                                                               |

| 3 | Enh | anced Port Processor                                                                                                                                                                                                                            |

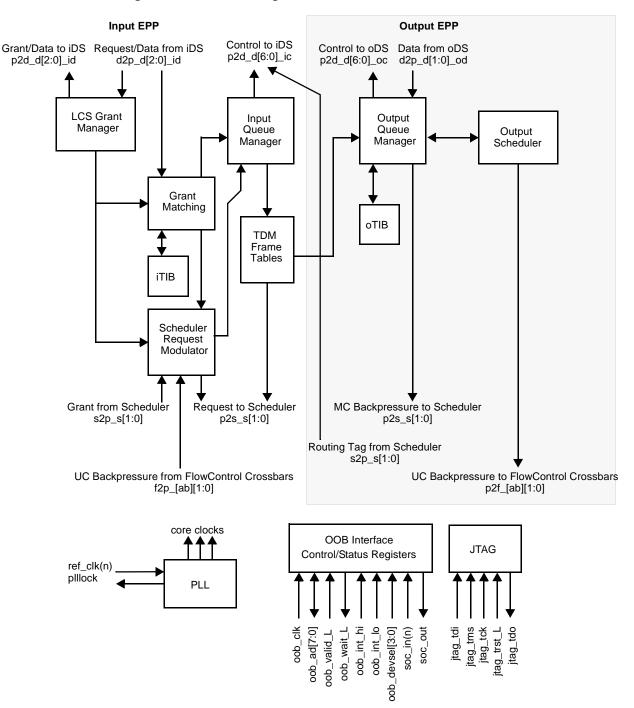

|   | 3.1 | EPP Data Flows and Blocks1533.1.1EPP Data Flows1543.1.2LCS Grant Manager1563.1.3Scheduler Request Modulator1583.1.4Input Queue Manager1593.1.5Output Queue Manager1603.1.6Output Scheduler1613.1.7OOB Interface and Control/Status Registers161 |

|   | 3.2 | Input Dataslice Queue Memory Allocation with EPP                                                                                                                                                                                                |

|   | 3.3 | Output Dataslice Queue Memory Allocation with EPP                                                                                                                                                                                               |

|   | 3.4 | Enhanced Port Processor Registers       165         3.4.1       Enhanced Port Processor Summary       165                                                                                                                                       |

|   |     | 3.4.2 Enhanced Port Processor Register Descriptions                                                                                                                                                                                             |

|   | 3.5 | Enhanced Port processor Signal Descriptions                                                                                                                                                                                                     |

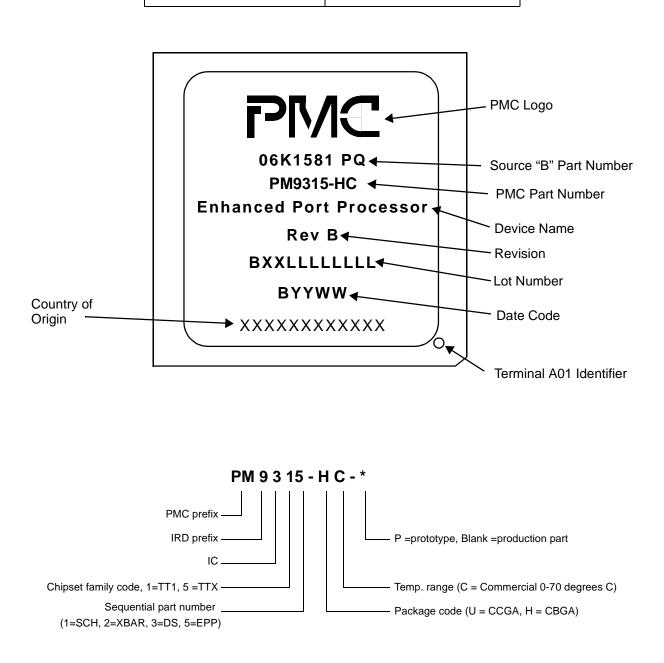

|   | 3.6 | Pinout and Package Information2143.6.1Pinout Tables2143.6.2Package Dimensions2213.6.3Part Number223                                                                                                                                             |

| 4 | Cro | ssbar                                                                                                                                                                                                                                           |

|   | 4.1 | Crossbar Blocks                                                                                                                                                                                                                                 |

|   | 4.2 | Modes Of Operation 227                                                                                                                                                                                                                          |

|   | 4.3 | OOB Access                                                                                                                                                                                                                                      |

|   | 4.4 | Crossbar Registers2284.4.1Summary2284.4.2Crossbar Register Descriptions229                                                                                                                                                                      |

|   | 4.5 | Crossbar Signal Descriptions 237                                                                                                                                                                                                                |

ISSUE 3

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

| Data | Sheet |

|------|-------|

| Dala | Sneer |

PMC-2000164

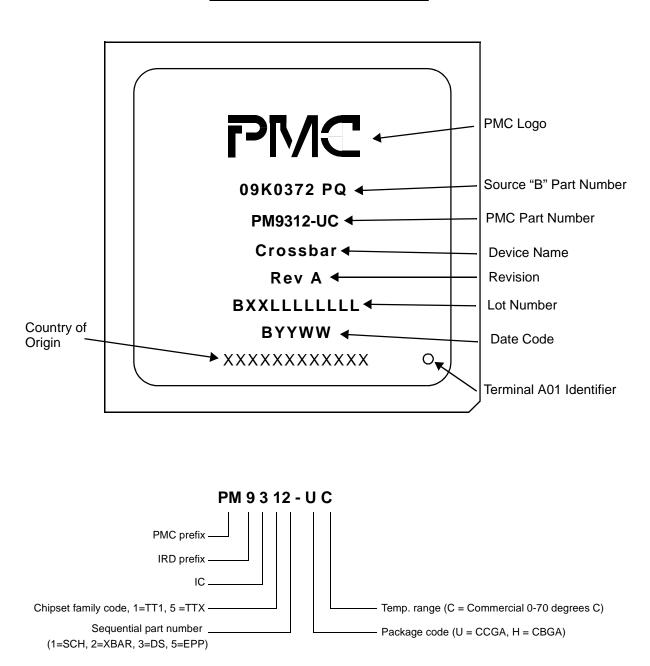

|    | 4.6   | Pinout and Package Information       240         4.6.1       Pinout Tables       240           |

|----|-------|------------------------------------------------------------------------------------------------|

|    |       | 4.6.1         Pinout Tables         240           4.6.2         Package Dimensions         249 |

|    |       | 4.6.2         Package Dimensions         249           4.6.3         Part Number         251   |

| 5  | Sch   | eduler                                                                                         |

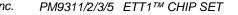

|    | 5.1   | Block Structure                                                                                |

|    |       | 5.1.1 Port Block                                                                               |

|    |       | 5.1.2 Arbiter Block                                                                            |

|    |       | 5.1.3 OOB Interface and Control/Status Registers                                               |

|    |       | 5.1.4 TDM Service                                                                              |

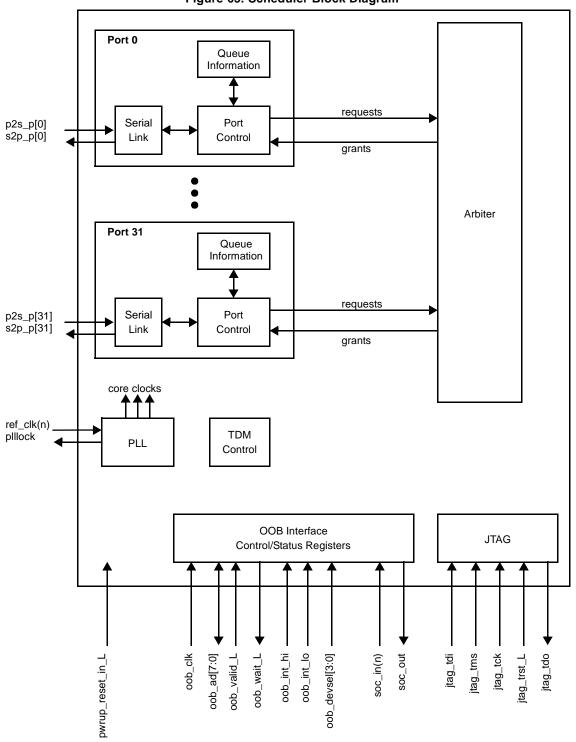

|    | 5.2   | Port State                                                                                     |

|    | 5.3   | Fault Tolerance                                                                                |

|    | 5.4   | Scheduler Registers 259                                                                        |

|    |       | 5.4.1 Summary                                                                                  |

|    |       | 5.4.2 Scheduler Register Descriptions                                                          |

|    |       | 5.4.3 Input Queue Memory (IQM)                                                                 |

|    | 5.5   | Scheduler Signal Descriptions 276                                                              |

|    | 5.6   | Pinout and Package Information 279                                                             |

|    |       | 5.6.1 Pinout Tables                                                                            |

|    |       | 5.6.2 Package Dimensions                                                                       |

|    |       | 5.6.3 Part Number                                                                              |

| 6  | Cha   | racteristics                                                                                   |

|    | 6.1   | Signal Associations                                                                            |

|    | 6.2   | Absolute Maximum Ratings 297                                                                   |

|    | 6.3   | Recommended Operating Conditions 299                                                           |

|    | 6.4   | DC Electrical Characteristics 302                                                              |

|    | 6.5   | AC Electrical Characteristics 305                                                              |

|    | 6.6   | Timing Diagrams                                                                                |

| Ap | pendi | x A General Packet/Frame Formats                                                               |

Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

ISSUE 3

| A.1<br>A.2<br>A.3        | Frame Formats - Dataslice To and From Enhanced Port Processor 317<br>Frame Formats - Dataslice To and From Crossbar                                                                                        |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendi                  | x B Common Pinout Configuration                                                                                                                                                                            |

| B.1<br>B.2<br>B.3<br>B.4 | JTAG Interface323Reserved Manufacturing Test Pins323Power Supply Connections324Example Power Up Sequence325                                                                                                |

| Appendi                  | x C Interfacing Details for ETT1 327                                                                                                                                                                       |

| C.1                      |                                                                                                                                                                                                            |

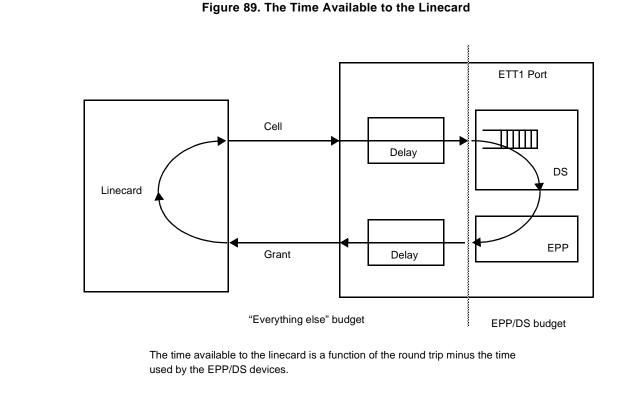

|                          | C.1.1 Preventing Underflow of the VOQ                                                                                                                                                                      |

| C.2                      | C.1.1         Preventing Underflow of the VOQ         327           The 8b/10b Interface to the Dataslice         328           C.2.1         Link         329           C.2.2         Channel         333 |

| C.2<br>C.3               | The 8b/10b Interface to the Dataslice                                                                                                                                                                      |

Data Sheet

PMC-2000164

ISSUE 3

Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

ISSUE 3

| Figure 1.  | The Basic Components of a Switch Built Around the ETT1 Chip Set                   |

|------------|-----------------------------------------------------------------------------------|

| Figure 2.  | ETT1 Switch Core Logical Interconnects                                            |

| Figure 3.  | Two Port Configuration of a ETT1 Switch   20                                      |

| Figure 4.  | Queueing and Flow Control                                                         |

| Figure 5.  | The TDM Frame Concept                                                             |

| Figure 6.  | Fully Redundant Core    26                                                        |

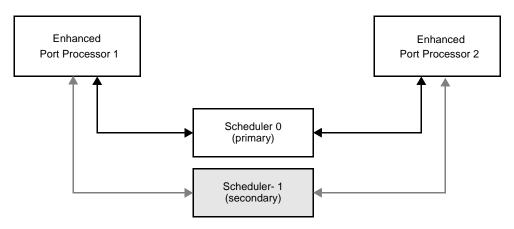

| Figure 7.  | Simple Redundant Scheduler Configuration                                          |

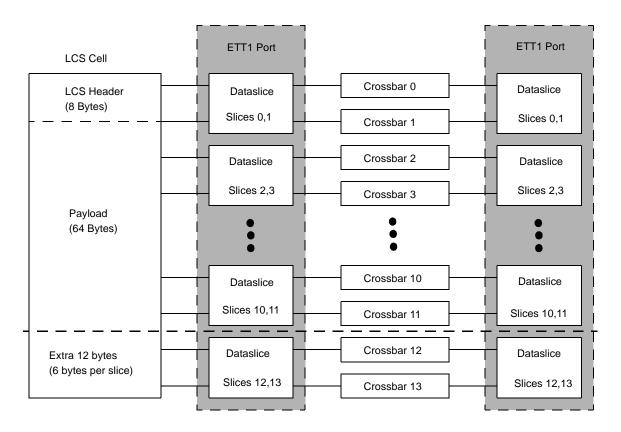

| Figure 8.  | LCS Cell Sliced Across Dataslices and Crossbars                                   |

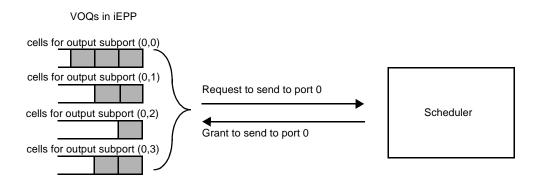

| Figure 9.  | The Unicast Ingress Queueing Model for One Port                                   |

| Figure 10. | Ingress and Egress Queue for Multicast Traffic                                    |

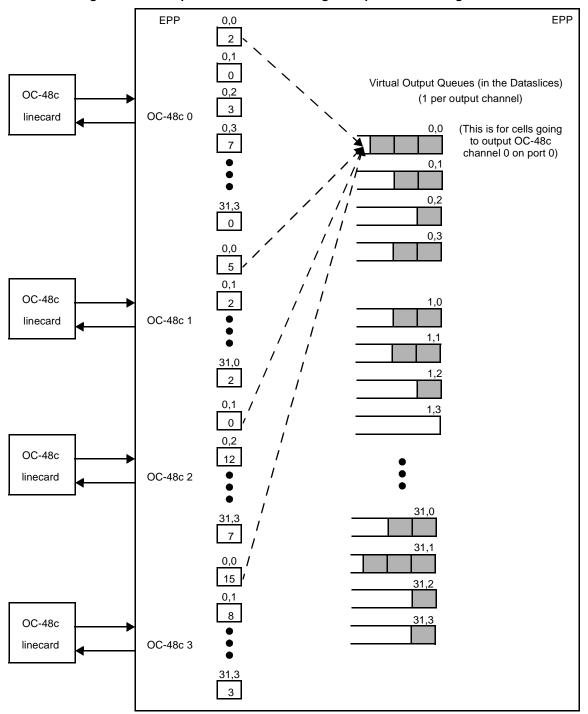

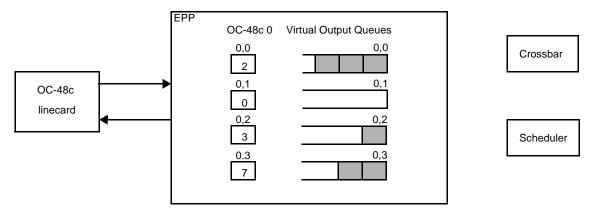

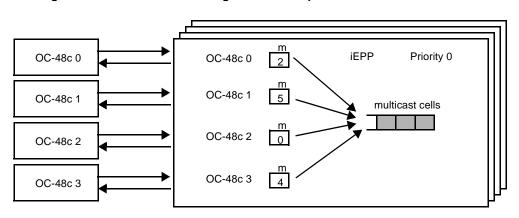

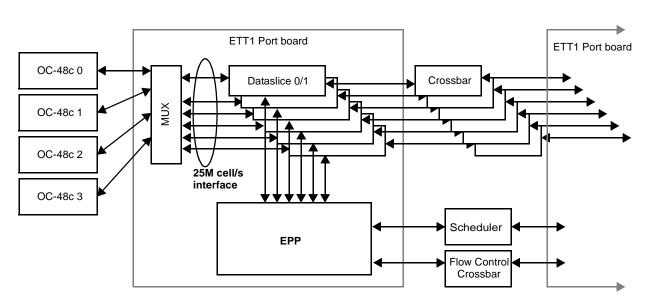

| Figure 11. | An ETT1 Port Operating in Subport Mode with Four OC-48c Linecards                 |

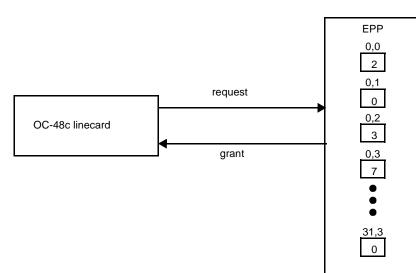

| Figure 12. | The Input Request Counters                                                        |

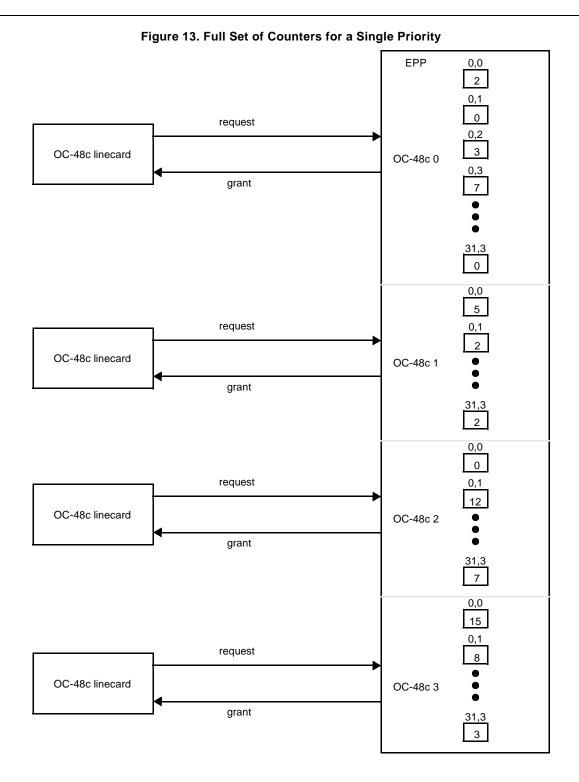

| Figure 13. | Full Set of Counters for a Single Priority    36                                  |

| Figure 14. | All Request Counters for a Single Output Share a Single Queue                     |

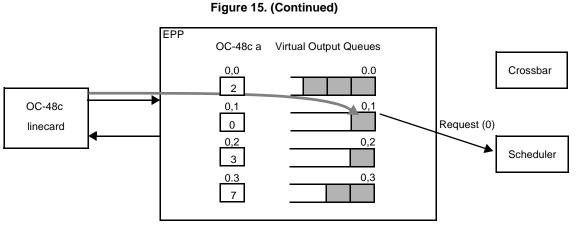

| Figure 15. | Sequence of Events at the Input Side 40                                           |

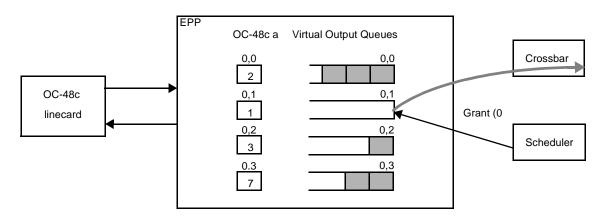

| Figure 16. | Virtual Input Queues                                                              |

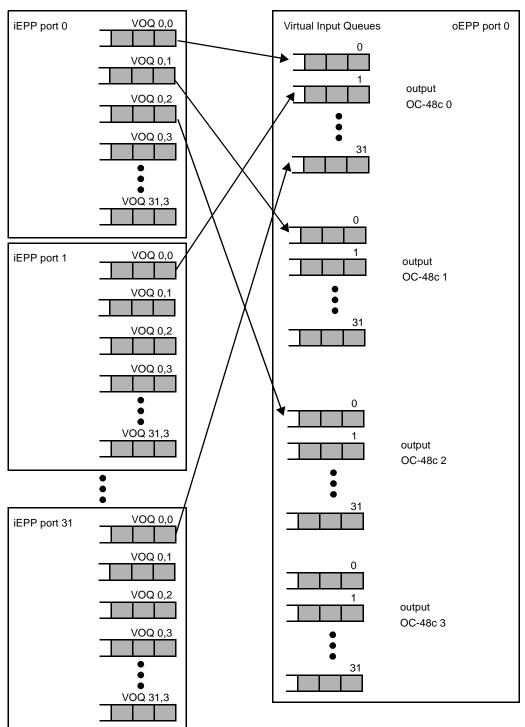

| Figure 17. | The Four Priorities                                                               |

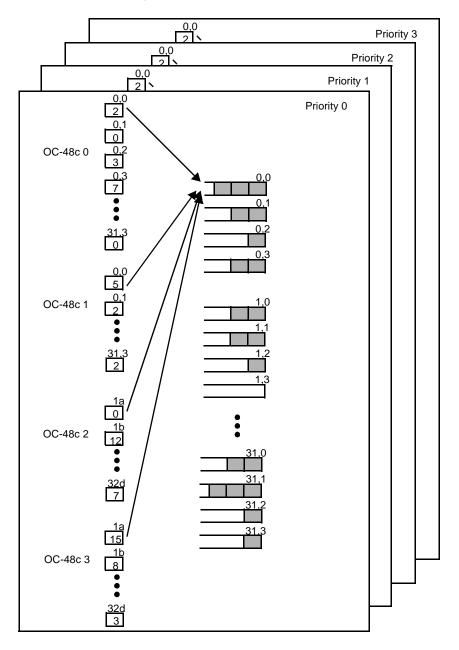

| Figure 18. | Scheduler Requests/Grants are Multiplexed at a Port Level                         |

| Figure 19. | Each iEPP has a Single Virtual Output Queue for Multicast Cells                   |

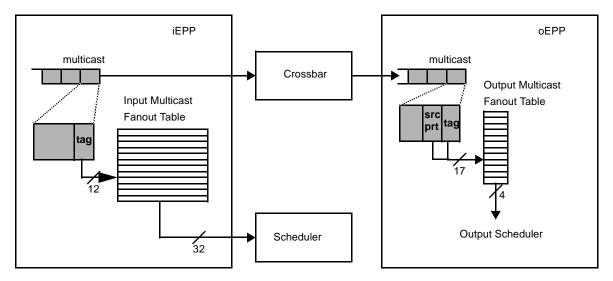

| Figure 20. | Multicast Cell Processing                                                         |

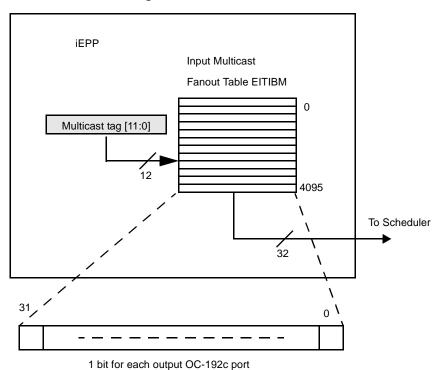

| Figure 21. | EITIBM structure                                                                  |

| Figure 22. | OITIBM structure                                                                  |

| Figure 23. | Scheduler Priorities                                                              |

| Figure 24. | ETT1 Port Ingress Queues                                                          |

| Figure 25. | A Separate Crossbar is Used to Convey Backpressure Information to the iEPPs 53    |

| Figure 26. | The Queueing Structure                                                            |

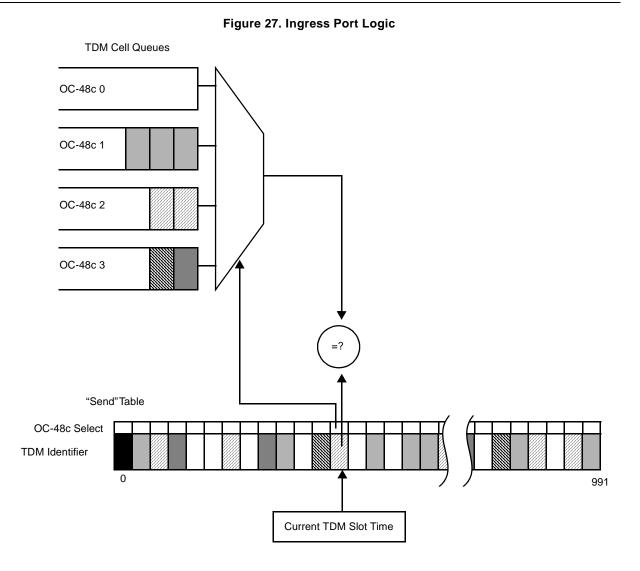

| Figure 27. | Ingress Port Logic                                                                |

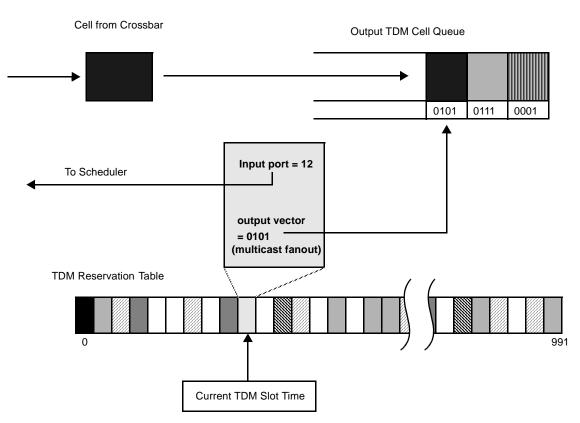

| Figure 28. | The oEPP Must Treat the Transferred TDM Cell as a Multicast Cell                  |

| Figure 29. | Single TDM Table                                                                  |

| Figure 30. | TDM Synchronization                                                               |

| Figure 31. | Signal Flow                                                                       |

| Figure 32. | One Implementation: The OOB Bus Consists of Both Local and Global Buses           |

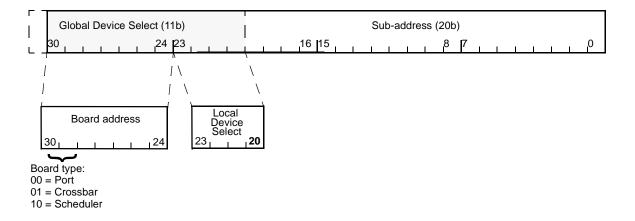

| Figure 33. | The Global Device Select Defines the Board Number and the Device on Each Board 80 |

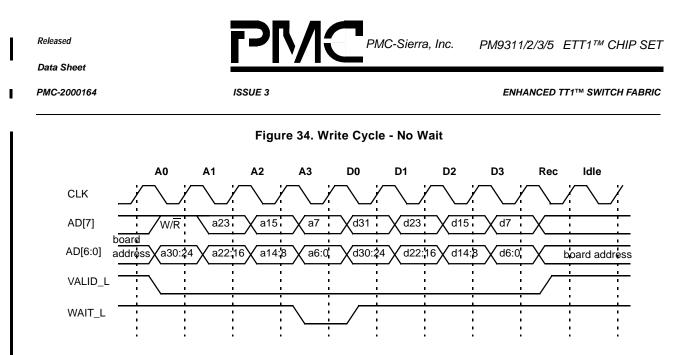

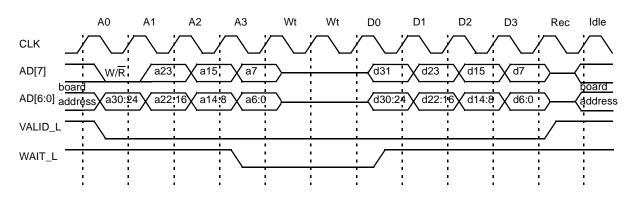

| Figure 34. | Write Cycle - No Wait                                                             |

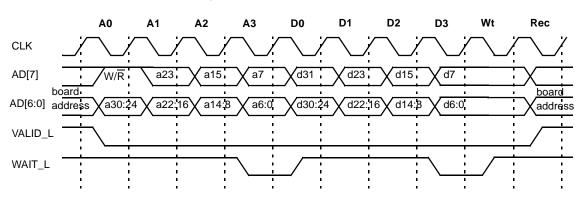

| Figure 35. | Write Cycle - One Wait                                                            |

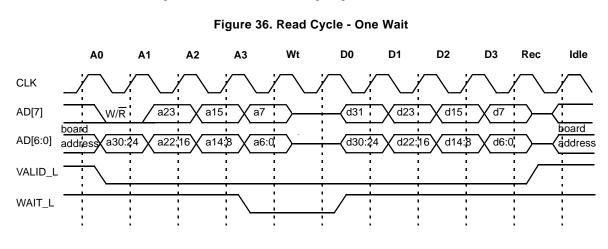

| Figure 36. | Read Cycle - One Wait                                                             |

| Figure 37. | Read Cycle - Two Waits                                                            |

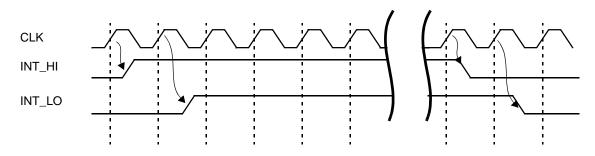

| Figure 38. | Interrupts are Active High and Synchronous                                        |

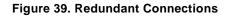

| Figure 39. | Redundant Connections                                                             |

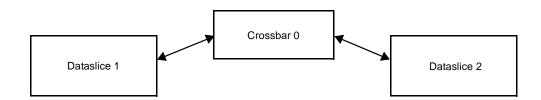

| Figure 40. | Simple Non-Redundant Crossbar Configuration                                       |

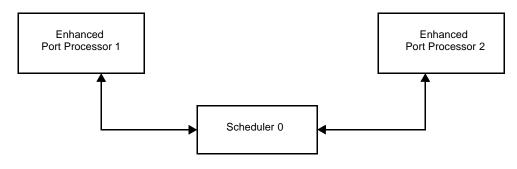

| Figure 41. | Simple Non-Redundant Scheduler Configuration                                      |

Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

ISSUE 3

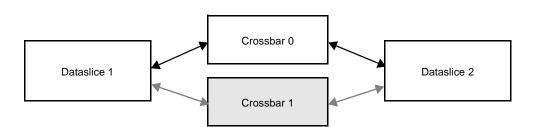

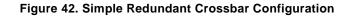

| Figure 42.               | Simple Redundant Crossbar Configuration                                                                                            |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Figure 43.               | Simple Redundant Scheduler Configuration                                                                                           |

| Figure 44.               | ETT1 Signals and Interconnects 102                                                                                                 |

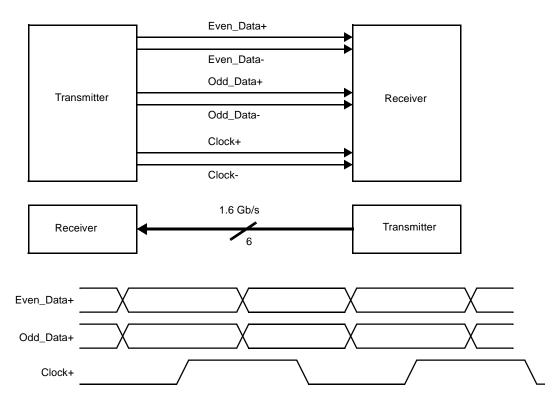

| Figure 45.               | AIB Links                                                                                                                          |

| Figure 46.               | AIB Control/Status Signals                                                                                                         |

| Figure 47.               | Request to Grant latency                                                                                                           |

| Figure 48.               | ETT1 Event Latencies                                                                                                               |

| Figure 49.               | Cell Latency                                                                                                                       |

| Figure 50.               | Illustrating the Flow of Cells from the Linecard CPU to the ETT1 CPU                                                               |

| Figure 51.               | Loopback Path                                                                                                                      |

| Figure 52.               | Control Packet Exchange Between Linecard CPU and ETT1 CPU                                                                          |

| Figure 53.               | Testing the ETT1 Internal Datapaths 113                                                                                            |

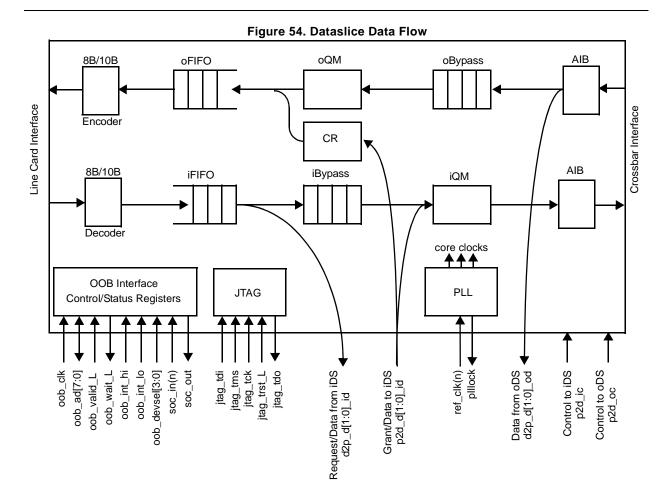

| Figure 54.               | Dataslice Data Flow                                                                                                                |

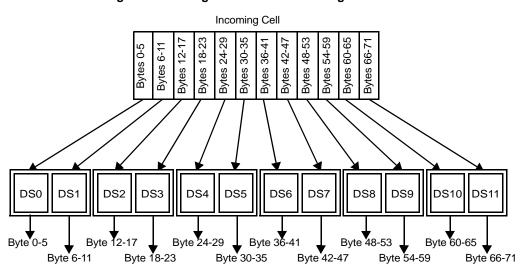

| Figure 55.               | Slicing of a Data Cell into Logical Dataslices                                                                                     |

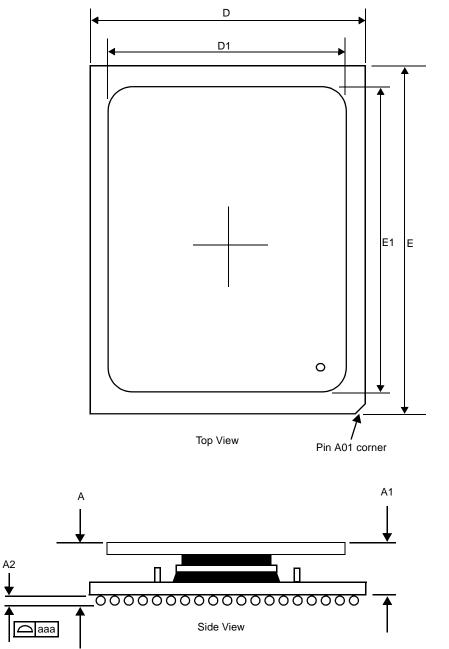

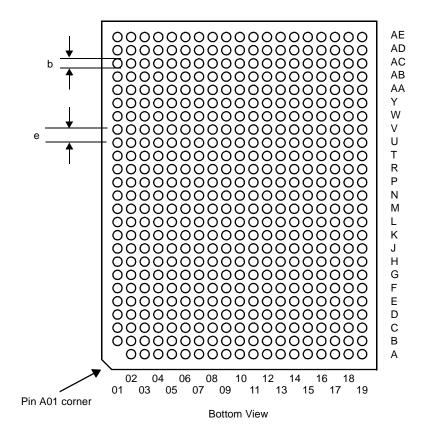

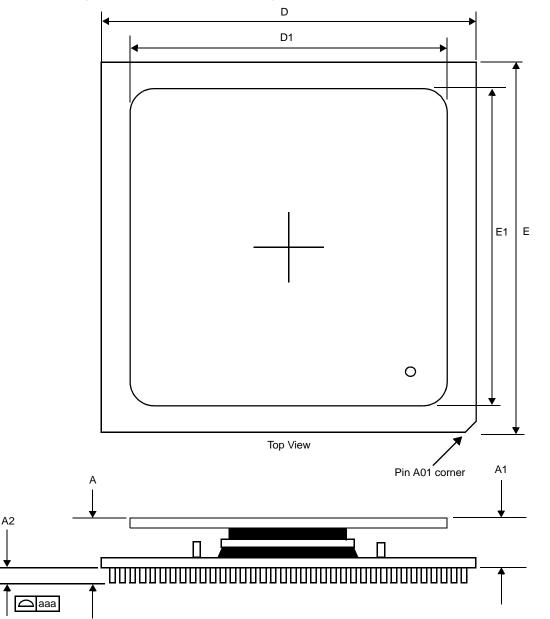

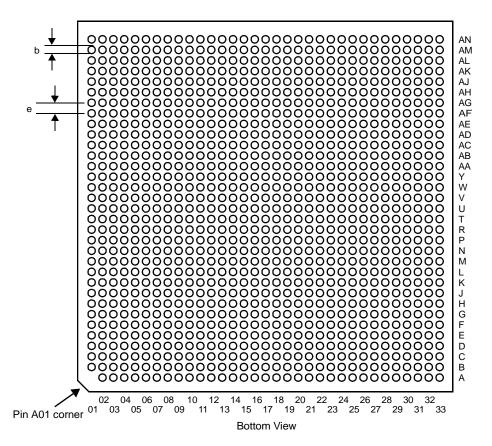

| Figure 56.               | Dataslice CBGA Package Dimensions - Top and Side Views                                                                             |

| Figure 57.               | Dataslice CBGA Package Dimensions - Bottom View                                                                                    |

| Figure 58.               | An ETT1 Port Operating in Sub-port Mode with Four OC-48c Linecards                                                                 |

| Figure 59.               | Functional Diagram of LCS Enhanced Port Processor                                                                                  |

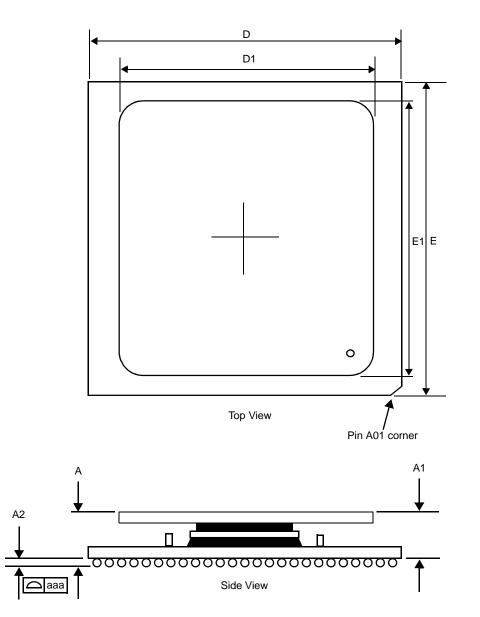

| Figure 60.               | Enhanced Port Processor CBGA Package Dimensions - Top and Side Views                                                               |

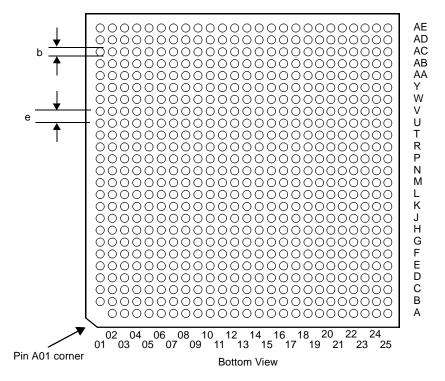

| Figure 61.               | Enhanced Port Processor (EPP) CBGA Package Dimensions - Bottom View                                                                |

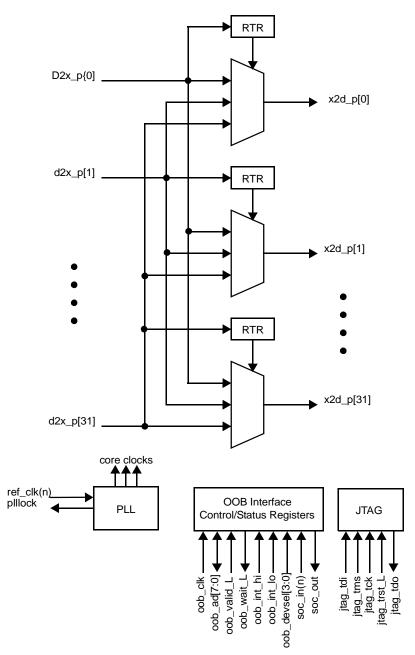

| Figure 62.               | The Basic Dataflow Through the Crossbar                                                                                            |

| Figure 63.               | Crossbar CCGA Package Dimensions - Top and Side Views                                                                              |

| Figure 64.               | Crossbar CCGA package Dimensions - Bottom View                                                                                     |

| Figure 65.               | Scheduler Block Diagram                                                                                                            |

| Figure 66.               | Port State Machine. 256                                                                                                            |

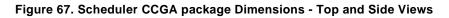

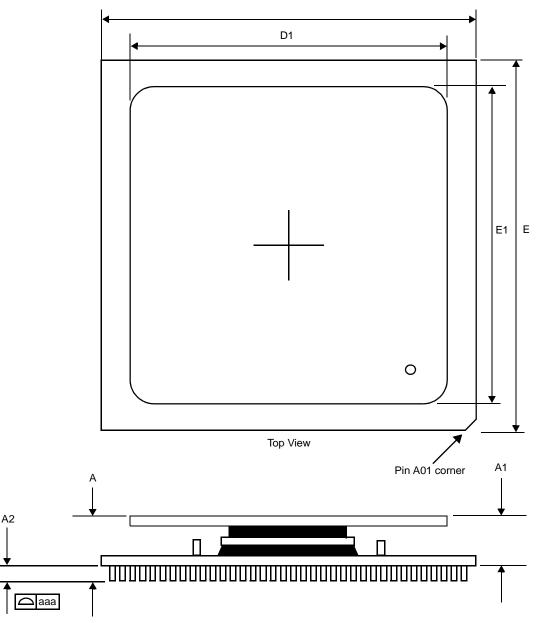

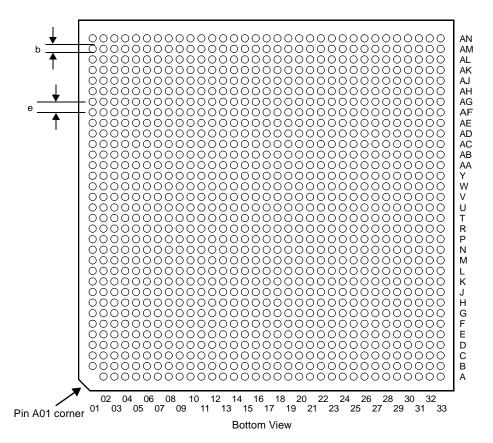

| Figure 67.               | Scheduler CCGA package Dimensions - Top and Side Views                                                                             |

| Figure 68.               | Scheduler CCGA package Dimensions - Bottom View                                                                                    |

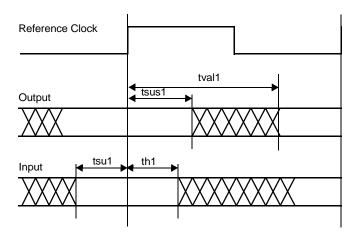

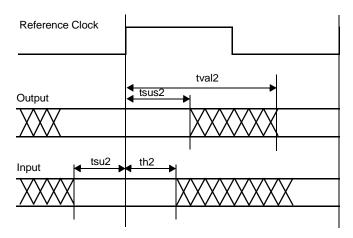

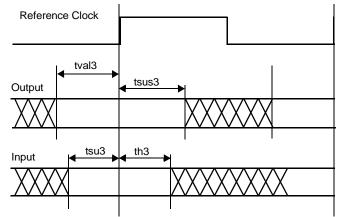

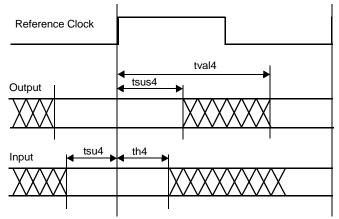

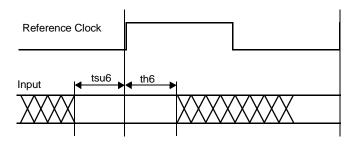

| Figure 69.               | Setup and Hold for 3.3V-tolerant 2.5V CMOS and 2.5V CMOS (OOB Interface)                                                           |

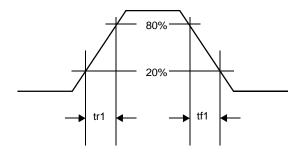

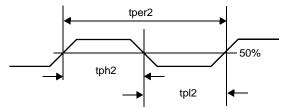

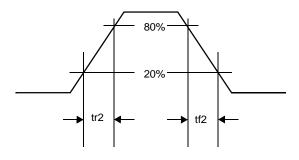

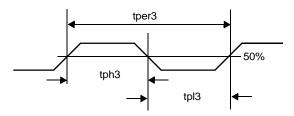

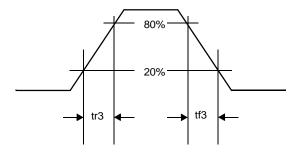

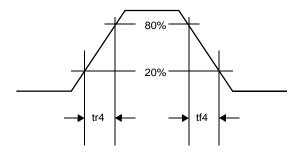

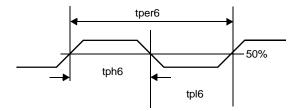

| Figure 70.               | Rise and Fall Times for 3.3V-tolerant 2.5V CMOS and 2.5V CMOS (OOB Interface) 309                                                  |

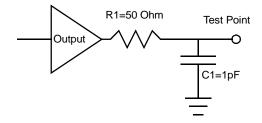

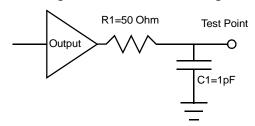

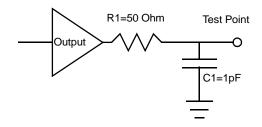

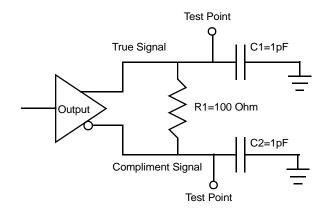

| Figure 71.               | OOB Test Loading                                                                                                                   |

| Figure 72.               | Setup and Hold for 3.3V-tolerant 2.5V CMOS and 2.5V CMOS (JTAG Interface) 310                                                      |

| Figure 73.               | Rise and Fall Times for 3.3V-tolerant 2.5V CMOS and 2.5V CMOS (JTAG Interface) 310                                                 |

| Figure 74.               | JTAG Test Loading                                                                                                                  |

| Figure 75.               | Setup and Hold for 3.3V-tolerant 2.5V CMOS and 2.5V CMOS (Serdes Interface) 311                                                    |

| Figure 76.               | Rise and Fall Times for 3.3V-tolerant 2.5V CMOS and 2.5V CMOS (Serdes Interface) 311                                               |

| Figure 77.               | Serdes Test Loading                                                                                                                |

| Figure 78.               | Setup and Hold for 200 Mbps HSTL (EPP/DS Interface)                                                                                |

| Figure 79.               | Rise and Fall Times for 200 Mbps HSTL (EPP/DS Interface)                                                                           |

| Figure 80.               | Class 1 HSTL Test Loading                                                                                                          |

| -                        |                                                                                                                                    |

| 0                        |                                                                                                                                    |

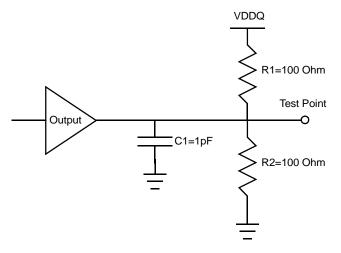

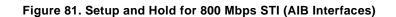

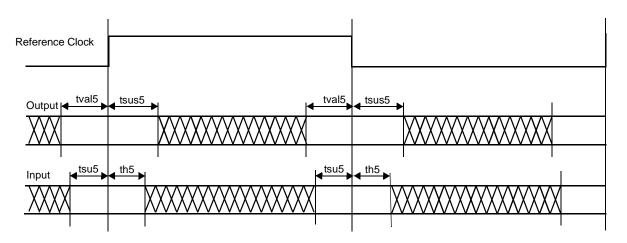

| Figure 81.<br>Figure 82. | Setup and Hold for 800 Mbps STI (AIB Interfaces)       314         Rise and Fall Times for 800 Mbps STI (AIB Interfaces)       314 |

Data Sheet

PMC-2000164

ISSUE 3

| Figure 83. | AIB Test Loading                                                |

|------------|-----------------------------------------------------------------|

| Figure 84. | Setup and Hold for 2.5V 200 Mbps PECL (CLK & SOC Signals)       |

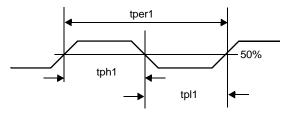

| Figure 85. | Clock Period and Duty Cycle for 2.5V 200 Mbps PECL (CLK Signal) |

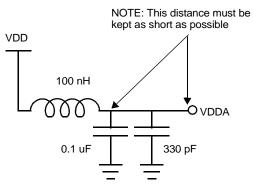

| Figure 86. | Example Noise Isolation Circuit                                 |

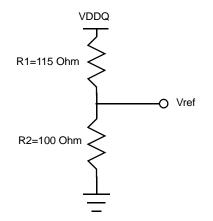

| Figure 87. | Example Voltage Divider                                         |

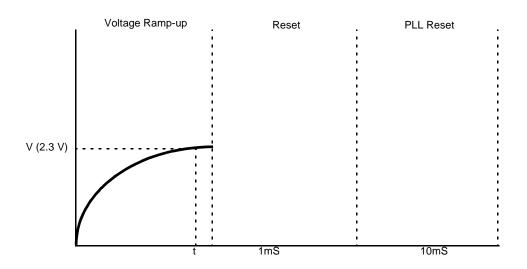

| Figure 88. | Voltage Ramp-up                                                 |

| Figure 89. | The Time Available to the Linecard                              |

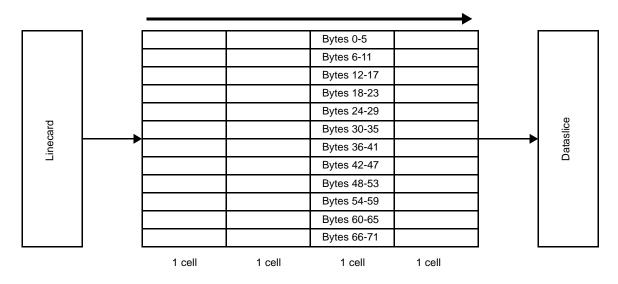

| Figure 90. | Cells are Striped Across the 12 Physical Links                  |

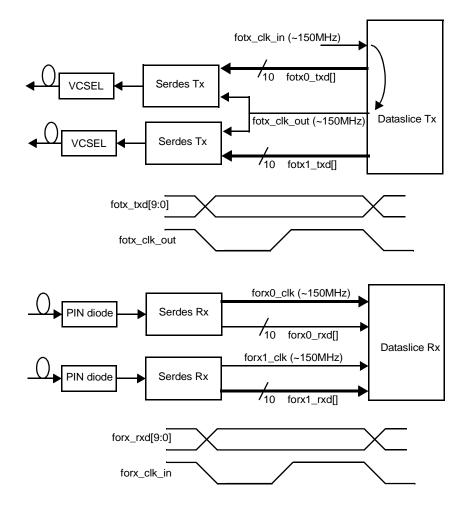

| Figure 91. | The 10-bit Data Paths                                           |

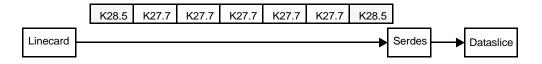

| Figure 92. | Initial Sequence Expected at Port Card                          |

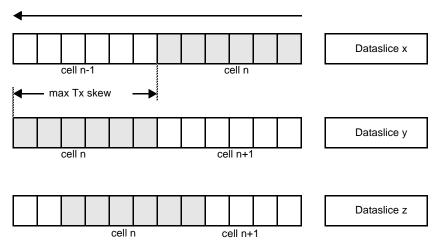

| Figure 93. | Cells May Be Skewed Between Dataslices                          |

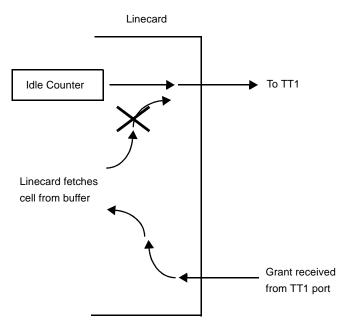

| Figure 94. | The Idle Counter Can Delay an Outbound Cell                     |

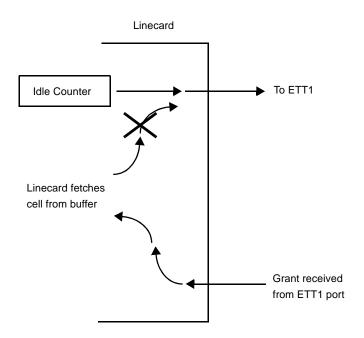

| Figure 95. | The Idle Counter Can Delay an Outbound Cell                     |

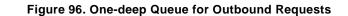

| Figure 96. | One-deep Queue for Outbound Requests                            |

Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

ISSUE 3

Data Sheet

PMC-2000164

ISSUE 3

| Table 1.       Crossbar Configurations         Table 2.       TDM Reservation Table         Table 3.       LCS Format from Linecard to Switch         Table 4.       Definitions of LCS Fields from Linecard to Switch         Table 5.       LCS Format from Switch to Linecard | 55<br>65<br>66<br>66<br>67<br>67 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Table 3.LCS Format from Linecard to SwitchTable 4.Definitions of LCS Fields from Linecard to SwitchTable 5.LCS Format from Switch to Linecard                                                                                                                                    | 65<br>65<br>66<br>66<br>67<br>67 |

| Table 4.Definitions of LCS Fields from Linecard to SwitchTable 5.LCS Format from Switch to Linecard                                                                                                                                                                              | 65<br>66<br>66<br>67<br>67       |

| Table 5.         LCS Format from Switch to Linecard                                                                                                                                                                                                                              | 66<br>66<br>67<br>67             |

|                                                                                                                                                                                                                                                                                  | 66<br>67<br>67                   |

|                                                                                                                                                                                                                                                                                  | 67<br>67                         |

| Table 6.         Definitions of LCS Fields from Switch to Linecard                                                                                                                                                                                                               | 67                               |

| Table 7.         Encoding of 4-bit Type Fields                                                                                                                                                                                                                                   |                                  |

| Table 8.    Usage of the Ingress Request Label_1                                                                                                                                                                                                                                 | 68                               |

| Table 9.    Usage of the Egress Grant Label_1                                                                                                                                                                                                                                    |                                  |

| Table 10.    Usage of the Egress Payload Label_2                                                                                                                                                                                                                                 |                                  |

| Table 11.    LCS Control Packet Format                                                                                                                                                                                                                                           |                                  |

| Table 12.    TDM Control Packet Format                                                                                                                                                                                                                                           |                                  |

| Table 13.    Request Count Control Packet Format                                                                                                                                                                                                                                 |                                  |

| Table 14.    Start/Stop Control Packet Format                                                                                                                                                                                                                                    |                                  |

| Table 15.    Fiber 1.5 Gbit/s per Channel Interface Configurations                                                                                                                                                                                                               | 76                               |

| Table 16.    Mapping Segments to 1.5 Gbit/s Channels                                                                                                                                                                                                                             | 76                               |

| Table 17.    OOB Control Bus Signals                                                                                                                                                                                                                                             | 78                               |

| Table 18.   Multicast Group Selects                                                                                                                                                                                                                                              | 79                               |

| Table 19.   Unicast Group Selects                                                                                                                                                                                                                                                | 81                               |

| Table 20.    Refresh-sensitive Registers in the Scheduler                                                                                                                                                                                                                        | 99                               |

| Table 21.    Dataslice Register Summary                                                                                                                                                                                                                                          | 119                              |

| Table 22.    Dataslice Signal Descriptions                                                                                                                                                                                                                                       | 136                              |

| Table 23.    Dataslice Pinout (left side)                                                                                                                                                                                                                                        | 142                              |

| Table 24.    Dataslice Pinout (right side)                                                                                                                                                                                                                                       | 143                              |

| Table 18.   Dataslice Alpha Pin List                                                                                                                                                                                                                                             | 144                              |

| Table 19.    Dataslice CBGA Mechanical Specifications                                                                                                                                                                                                                            | 148                              |

| Table 20.    Linecard Request Count Maximum Values                                                                                                                                                                                                                               | 157                              |

| Table 21.    Input Dataslice Queue Memory Allocation                                                                                                                                                                                                                             | 162                              |

| Table 22.    Output Dataslice Queue Memory Allocation                                                                                                                                                                                                                            | 163                              |

| Table 23.         EPP Egress Control Packet Data Format and Dataslice OOB Addressing                                                                                                                                                                                             | 164                              |

| Table 24.    Enhanced Port Processor Register Summary                                                                                                                                                                                                                            |                                  |

| Table 25.    Enhanced Port Processor Signal Descriptions                                                                                                                                                                                                                         | 209                              |

| Table 26.    Enhanced Port Processor Pinout (left side)                                                                                                                                                                                                                          |                                  |

| Table 27.    Enhanced Port Processor Pinout (center)                                                                                                                                                                                                                             |                                  |

| Table 28.       Enhanced Port Processor Pinout (right side)                                                                                                                                                                                                                      |                                  |

| Table 35.       Enhanced Port Processor Alpha Pin List                                                                                                                                                                                                                           |                                  |

| Table 36. Enhanced Port Processor CBGA Mechanical Specifications                                                                                                                                                                                                                 |                                  |

| Table 37.   Crossbar Register Summary                                                                                                                                                                                                                                            |                                  |

| Table 38.     Crossbar Signal Descriptions                                                                                                                                                                                                                                       |                                  |

| Table 39.     Crossbar Pinout (left side)                                                                                                                                                                                                                                        |                                  |

| Table 40.       Crossbar Pinout (center)                                                                                                                                                                                                                                         |                                  |

Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1<sup>TM</sup> CHIP SET

ISSUE 3

| Table 41. | Crossbar Pinout (right side)                                                      |

|-----------|-----------------------------------------------------------------------------------|

| Table 33. | Crossbar Alpha Pin List                                                           |

| Table 34. | Crossbar CCGA Mechanical Specifications                                           |

| Table 35. | Non-TDM Traffic                                                                   |

| Table 36. | Scheduler Register Summary 259                                                    |

| Table 37. | Scheduler Signal Descriptions                                                     |

| Table 38. | Scheduler Pinout (left side)                                                      |

| Table 39. | Scheduler Pinout (center)                                                         |

| Table 40. | Scheduler Pinout (right side) 281                                                 |

| Table 41. | Scheduler Alpha Pin List                                                          |

| Table 42. | Scheduler CCGA Mechanical Specifications                                          |

| Table 43. | Signal Associations                                                               |

| Table 44. | Absolute Maximum Ratings                                                          |

| Table 45. | Absolute Maximum Ratings for 3.3V-tolerant 2.5V CMOS (OOB & Serdes Interface) 297 |

| Table 46. | Absolute Maximum Ratings for 2.5V CMOS (JTAG Interface)                           |

| Table 47. | Absolute Maximum Ratings for 200 Mbps HSTL (EPP/DS Interface)                     |

| Table 48. | Absolute Maximum Ratings for 800 Mbps STI (AIB Interface)                         |

| Table 49. | Absolute Maximum Ratings for 2.5V 200 Mbps PECL (CLK and SOC Signals) 298         |

| Table 50. | Recommended Operating Conditions                                                  |

| Table 51. | Additional Power Design Requirements                                              |

| Table 52. | DC Electrical Characteristics for 3.3V-tolerant 2.5V CMOS (OOB Interface)         |

| Table 53. | DC Electrical Characteristics for 2.5V CMOS (JTAG Interface)                      |

| Table 54. | DC Electrical Characteristics for 3.3V-tolerant 2.5V CMOS (Serdes)                |

| Table 55. | DC Electrical Characteristics for 200 Mbps HSTL (EPP/DS Interface)                |

| Table 56. | DC Electrical Characteristics for 800 Mbps STI (AIB Interfaces)                   |

| Table 57. | DC Electrical Characteristics for 2.5V 200 Mbps PECL (CLK and SOC Signals)        |

| Table 58. | AC Electrical Characteristics for 3.3V-tolerant 2.5V CMOS (OOB Interface)         |

| Table 59. | AC Electrical Characteristics for 2.5V CMOS (JTAG Interface)                      |

| Table 60. | AC Electrical Characteristics for 3.3V-tolerant 2.5V CMOS (Serdes Interface)      |

| Table 61. | Reference Clock for 200 Mbps HSTL (EPP/DS Interface)                              |

| Table 62. | AC Electrical Characteristics for 800 Mbps STI (AIB Interface)                    |

| Table 63. | AC Electrical Characteristics for 2.5V 200Mbps PECL (CLK Signals)                 |

| Table 64. | Jitter and Static Phase Offset for PLL                                            |

| Table 65. | Request/Data from iDS Frame Format                                                |

| Table 66. | Data from oDS Frame Format                                                        |

| Table 67. | Grant/Data to iDS Frame Format                                                    |

| Table 68. | Control to xDS Link Format                                                        |

| Table 69. | Dataslice to Crossbar Frame Format                                                |

| Table 70. | Crossbar to Dataslice Frame Format                                                |

| Table 71. | Scheduler to EPP Frame Format                                                     |

| Table 72. | EPP to Scheduler Frame Format                                                     |

Released Data Sheet

PMC-2000164

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

Table 73.

Suggested 8b/10b Decode Map Within the Dataslice

331

Table 74.

Dataslice Egress Truth Table

331

Table 75.

Programmed Token Delay vs. Inter-link Skew

334

Data Sheet

PMC-2000164

PMC-Sierra, Inc. PM9311/2/3/5 ETT1™ CHIP SET

ISSUE 3

Data Sheet

I

PMC-2000164

PMC-Sierra, Inc.

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

# **1** Functional Description

## 1.1 OVERVIEW

The ETT1<sup>™</sup>Chip Set provides a crossbar-based switch core which is capable of switching cells between 32 ports with each port operating at data rates up to 10 Gbit/s. This section describes the main features of the switch core and how cells flow through a complete system that is based on the ETT1 Chip Set.

This document often refers to port rates of OC-192c or OC-48c. The ETT1 Chip Set itself operates at a fixed cell rate of 25M cells per second per port and thus is unaware of the actual data rate of the attached link. So a switch might be 32 ports of OC-192c, or it could be 32 ports of 10 Gbit/s Ethernet; it is the internal cell rate that is determined by the ETT1 Chip Set, not the link technology.

#### 1.1.1 ETT1 Switch Core Features

The ETT1 switch core provides the following features:

- 320 Gbit/s aggregate bandwidth up to 32 ports of 10 Gbit/s bandwidth each

- Each port can be configured as 4 x OC-48c or 1 x OC-192c

- Both port configurations support four priorities of best-effort traffic for unicast and multicast data traffic

- TDM support for guaranteed bandwidth and zero delay variation with 10 Mbit/s channel resolution

- LCS<sup>™</sup> protocol supports a physical separation of switch core and linecards up to 200 feet (70 m)

- Virtual output queues to eliminate head-of-line blocking on unicast cells

- Internal speedup to provide near-output-queued performance

- Cells are transferred using a credit mechanism to avoid cell losses due to buffer overrun

- In-band management and control via Control Packets

- Out-of-band management and control via a dedicated CPU interface

- Optional redundancy of all shared components for fault tolerance

- Efficient support for multicast with cell replication performed within the switch core

Data Sheet

PMC-2000164

PMC-Sierra, Inc.

. PM9311/2/3/5 ETT1™ CHIP SET

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

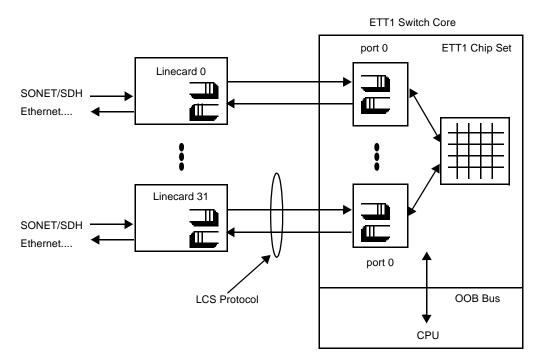

## 1.1.2 The Switch Core Model

The ETT1 Chip Set is designed to provide a switch core, not a complete packet switch system. A complete switch consists of one or more switch cores, together with a number of linecards. Each linecard connects to one port in the core. The linecard includes a physical interface (fiber, co-axial cable) to a transmission system such as SONET/SDH or Ethernet. The linecard analyzes incoming cells or packets and determines the appropriate egress port and priority. The linecard contains any cell/packet queues that are needed to allow for transient congestion through the switch.

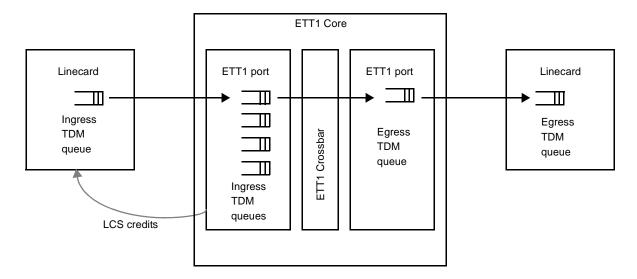

The ETT1 switch core operates on fixed size cells. If the linecard transmission system uses variable length packets, or cells of a size different from those used in the core, then the linecard is responsible for performing any segmentation and reassembly that is needed. Figure 1 illustrates this generic configuration.

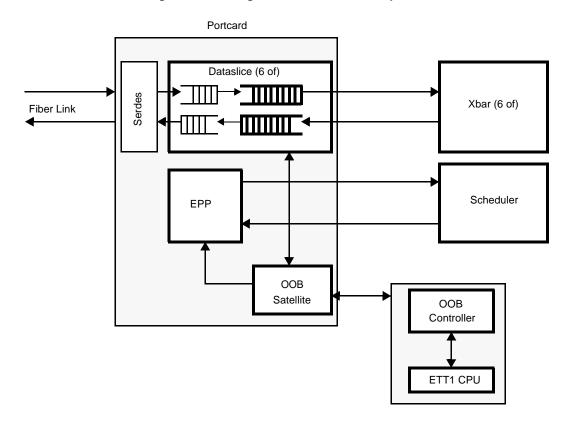

Figure 1. The Basic Components of a Switch Built Around the ETT1 Chip Set.

The ETT1 Chip Set has been designed to allow for up to 200 feet (70 meters) of physical separation between the ETT1 core and the linecard. The LCS™(Linecard to Switch) protocol is used between the ETT1 core and the linecard to ensure lossless transfer of cells between the two entities. However, while the LCS protocol must be implemented, the physical separation is not mandatory; the linecard could reside on the same physical board as the ETT1 port devices.

The switch core has two main interfaces. One is the interface between the linecard and the core port, described in the LCS Protocol section.

Data Sheet

I

PMC-2000164

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

The second interface is between the ETT1 devices and the local CPU. The ETT1 Chip Set requires a local CPU for configuration, diagnostics and maintenance purposes. A single CPU can control a complete ETT1 core via a common Out-Of-Band (OOB) bus. All of the ETT1 devices have an interface to the OOB bus. The OOB bus is described in Section 1.1.4 "The OOB (Out-Of-Band) Bus" on page 18.

#### 1.1.3 The LCS Protocol

The Linecard-to-Switch (LCS<sup>™</sup>) protocol provides a simple, clearly defined interface between the linecard and the core. In this section we introduce LCS. There are two aspects to LCS:

- a per-queue, credit-based flow control protocol

- a physical interface

The LCS protocol provides per-queue, credit-based flow control from the ETT1 core to the linecard, which ensures that queues are not overrun. The ETT1 core has shallow (64 cells) queues in both the ingress and egress directions. These queues compensate for the latency between the linecard and the core. One way to think of these queues is simply as extensions of the queues within the linecards. The queues themselves are described further in Section 1.3 "Prioritized Best-Effort Queue Model" on page 30.

The LCS protocol is asymmetrical; it uses different flow control mechanisms for the ingress and egress flows. For the ingress flow LCS uses credits to manage the flow of cells between the linecards and the ETT1 core. The core provides the linecard with a certain number of credits for each ingress queue in the core. These credits correspond to the number of cell requests that the linecard can send to the core. For each cell request that is forwarded to a given queue in the core the linecard must decrement the number of credits for that queue. The core sends a grant (which is also a new credit) to the linecard whenever the core is ready to accept a cell in response to the cell request. At some later time, which is dependent on the complete traffic load, the cell will be forwarded through the ETT1 core to the egress port. In the egress direction a linecard can send hole requests, requesting that the ETT1 core does *not* forward a cell for one celltime. The linecard can issue a hole request for each of the four best effort unicast or multicast priorities. If the linecard continually issued hole requests at all four priorities then the ETT1 core would not forward any best effort traffic to the linecard.

The LCS protocol information is contained within an eight byte header that is added to every cell.

The physical interface that has been implemented in the ETT1 Chip Set is based on a faster version of the Gigabit Ethernet Serdes interface, enabling the use of off-the-shelf parts for the physical link. This interface provides a

1.5 Gbit/s serial link that uses 8b/10b encoded data. Twelve of these links are combined to provide a single LCS link operating at 18 Gbaud, providing an effective data bandwidth that is in excess of an OC-192c link.

**NOTE:** The LCS protocol is defined in the "LCS Protocol Specification -- Protocol Version 2", available from PMC-Sierra, Inc. This version of LCS supersedes LCS Version 1. Version 2 is first supported in the TT1 Chip Set with the Enhanced Port Processor device (also referred to as the ETT1 Chip Set) and will be supported in future PMC-Sierra products.

The ETT1 implementation of the LCS protocol is described further in Section 1.6 "ETT1 Usage of the LCS Protocol" on page 64.

Data Sheet

PMC-2000164

PMC-Sierra, Inc.

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

### 1.1.4 The OOB (Out-Of-Band) Bus

The ETT1 Chip Set requires a local CPU to perform initialization and configuration after the Chip Set is reset or if the core configuration is changed - perhaps new ports are added or removed, for example. The OOB bus provides a simple mechanism whereby a local CPU can configure each device.

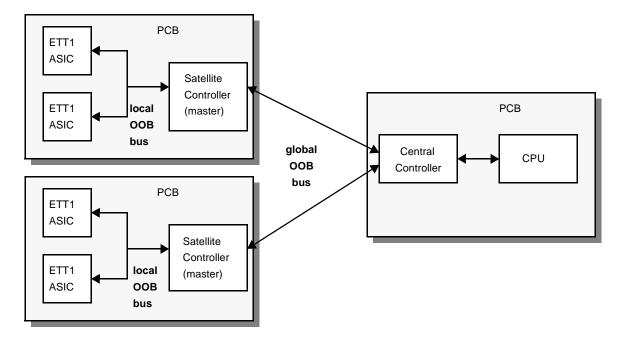

Logically, the OOB bus provides a 32 bit address/data bus with read/write, valid and ready signals. The purpose of the OOB bus is for maintenance and diagnostics; the CPU is not involved in any per-cell operations.

#### **1.2 ARCHITECTURE AND FEATURES**

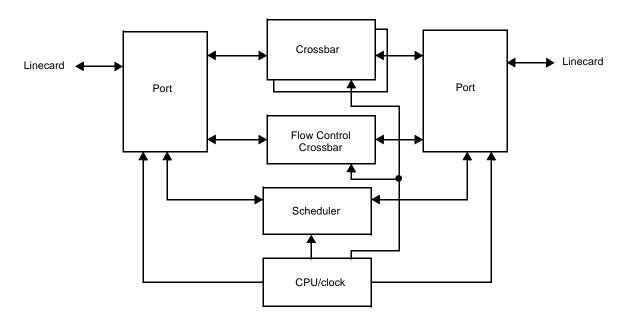

### 1.2.1 ETT1 Switch Core

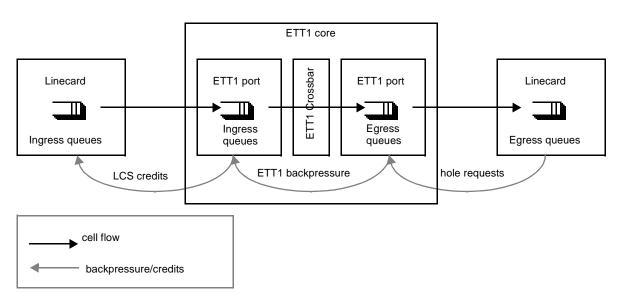

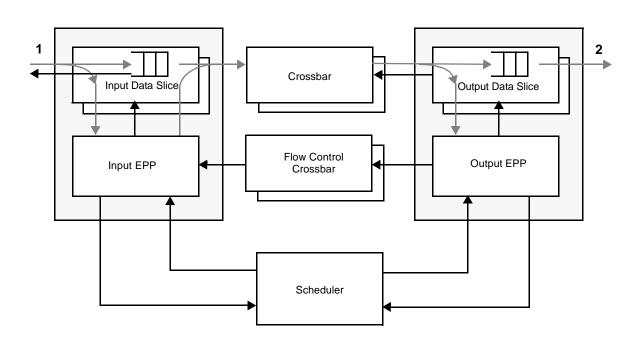

An ETT1 switch core consists of four types of entities: Port, Crossbar, Scheduler, and CPU/Clock. There may be one or more instances of each entity within a switch. For example, each entity might be implemented as a separate PCB, with each PCB interconnected via a single midplane PCB. Figure 2 illustrates the logical relationship between these entities.

#### Figure 2. ETT1 Switch Core Logical Interconnects

Data Sheet

PMC-2000164

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

Each ETT1 port is attached to one or more linecards. The port contains the shallow cell queues and implements the LCS protocol. The port and Scheduler exchange information about cells that are waiting to be forwarded through the Crossbar core.

The Scheduler maintains local information on the number of cells that are waiting in all of the ingress and egress queues. It arbitrates amongst all cells in the ingress queues, and instructs all of the ports as to which cell they can forward through the Crossbar at each cell time.

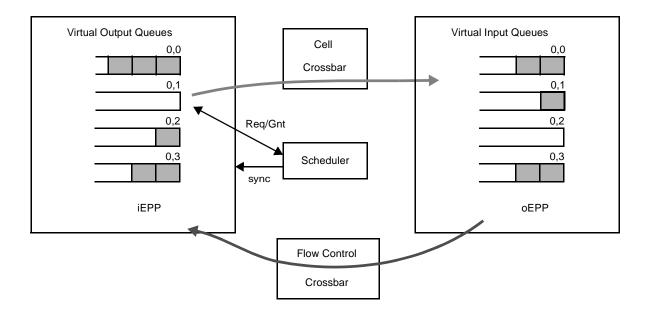

Two Crossbars are used. The first, referred to as simply 'the Crossbar', interconnects all of the ports with all of the other ports, enabling cells to be forwarded from the ingress port queues to the egress port queues (in a different port). The Crossbar is reconfigured at every cell time to provide any non-blocking one-to-one or one-to-many mapping from input ports to output ports. Each Crossbar port receives its configuration information from its attached port; the Crossbars do not communicate directly with the Scheduler. The second Crossbar is the flow-control Crossbar. It passes output queue occupancy information from every egress port to every ingress port. The ingress ports use this information to determine when requests should and should not be made to the Scheduler.

The CPU/clock provides clocks and cell boundary information to every ETT1 device. It also has a local CPU which can read and write state information in every ETT1 device via the OOB bus. The CPU/clock entity is a necessary element of the ETT1 switch core, but does not contain any of the ETT1 devices.

#### 1.2.2 Basic Cell Flow

The ETT1 Chip Set consists of four devices. Their names (abbreviations) are:

- Dataslice (DS)

- Enhanced Port Processor (EPP)

- Scheduler (Sched)

- Crossbar (Xbar)

This section describes how cells flow through these four devices.

Data Sheet

PMC-2000164

**ISSUE 3**

ENHANCED TT1™ SWITCH FABRIC

PMC-Sierra, Inc.

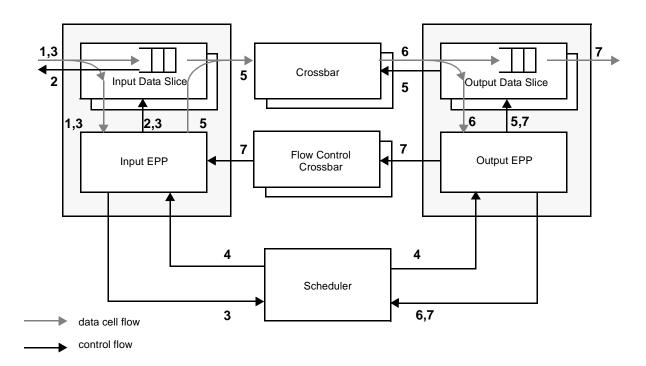

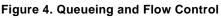

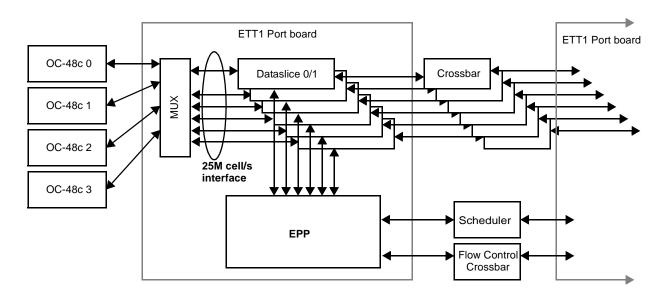

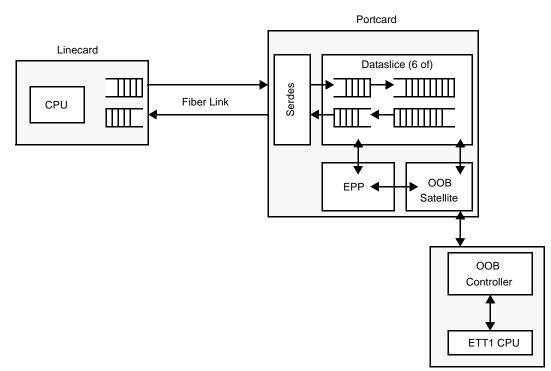

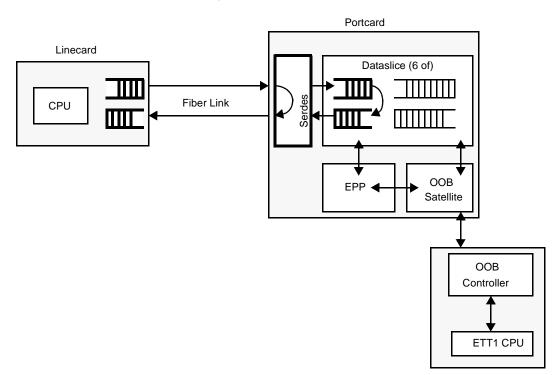

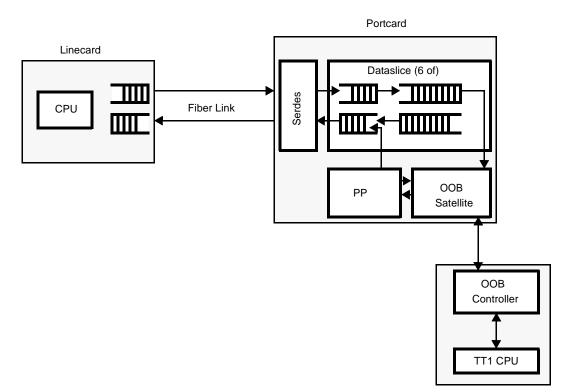

Figure 3 shows a two-port configuration of a ETT1 switch. Only the ingress queues of the left hand port and the egress queues of the right hand port are shown. The port has one EPP and either six or seven DS devices. The DS contains the cell queue memory and also has the Serdes interface to the linecard. A single cell is "sliced" across all of the Dataslice devices, each of which can manage two slices. The EPP is the port controller, and determines where cells should be stored in the DS memories. Multiple Crossbar devices make up a full Crossbar. A single Scheduler device can arbitrate for the entire core.

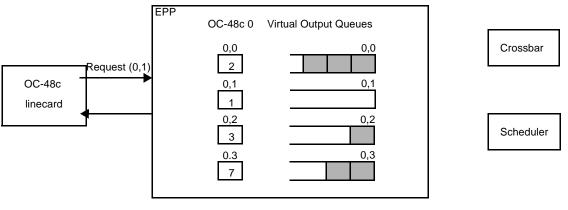

A cell traverses the switch core in the following sequence of events:

- 1. A cell request arrives at the ingress port, and is passed to the EPP. The EPP adds the request to any other outstanding cell requests for the same queue.

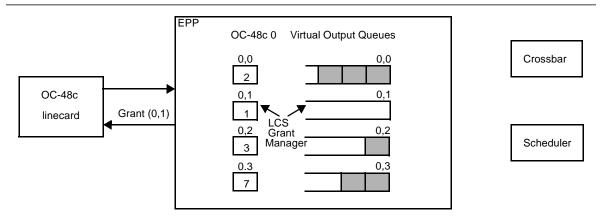

- 2. At some later time, the EPP issues a grant/credit to the source linecard, requesting an actual cell for a specific queue. The linecard must respond with the cell within a short period of time.

- 3. The cell arrives at the ingress port and the LCS header is passed to the EPP. The EPP determines the destination queue from the LCS header, and then tells the Dataslices where to store the cell (each Dataslice stores part of the cell). The EPP also informs the Scheduler that a new cell has arrived and so the Scheduler should add it to the list of cells waiting to be forwarded through the Crossbar. The EPP modifies the LCS label by replacing the destination port with the source port, so the egress port and linecard can see which port sent the cell.

- 4. The Scheduler arbitrates among all queued cells and sends a grant to those ports that can forward a cell. The Scheduler also sends a routing tag to each of the destination (egress) ports; this tag

I

I

I

I

Data Sheet PMC-2000164 PMC-Sierra, Inc.

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

tells the ports which of the many source ports will be sending it a cell.

- 5. The source EPP sends a read command to the Dataslices, which then reads the cell from the appropriate queue and sends it to the Crossbar. At the same time, the destination ports send the routing tag information to the Crossbar. This routing tag information is used to configure the internal connections within the Crossbar for the duration of one cell time. The cell then flows through the Crossbar from the source port to the destination port.

- 6. The cell arrives at the destination port, and the EPP receives the LCS header of the cell. It uses this information to decide in which egress queue the cell should be stored. If this was a multicast cell which caused the egress multicast to reach its occupancy limit, then the EPP would send a congestion notification to the Scheduler.

- 7. At some later time, the EPP decides to forward the cell to the linecard. The EPP sends a read command to the Dataslices which read the cell from memory and forward the cell out to the linecard. The egress EPP also sends flow control to the ingress EPP, informing it that there now exists free space in one or more of the egress EPP's output queues. Also, if the transmitted cell was a multicast cell then this may cause the egress queue to go from full to not full, in which case the EPP notifies the Scheduler that it (the EPP) can once again accept multicast cells.

The above description does not account for all of the interactions that can take place between ETT1 devices, but it describes the most frequent events. In general, users do not need to be aware of the detailed interactions, however knowledge of the main information flows will assist in gaining an understanding of some of the more complicated sections.

#### 1.2.3 Prioritized Best-effort Service

An ETT1 switch core provides two types of service. The first is a prioritized, best-effort service. The second provides guaranteed bandwidth and is described later.

The best-effort service is very simple. Linecards forward best-effort cells to the ETT1 core where they will be queued. The Scheduler arbitrates among the various cells; the arbitration algorithm has the dual goals of maximizing throughput while providing fair access to all ports. If more than one cell is destined for the same egress port then the Scheduler will grant one of the cells and the others will remain in their ingress queues awaiting another round of arbitration. The service is best-effort in that the Scheduler tries its best to satisfy all queued cells, but in the case of contention then some cells will be delayed.

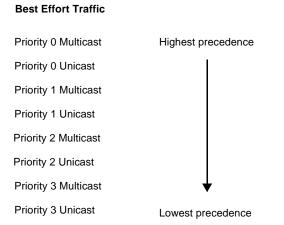

The Scheduler supports four levels of strict priority for best effort traffic. Level 0 cells have the highest priority, and level 3 cells have the lowest priority. A level 0 cell destined for a given port will always be granted before a cell of a different priority level, in the same ingress port, that is destined for the same egress port.

A 'flow' is a sequence of cells from the same ingress port to the same egress port(s) at a given priority. Best-effort flows are either unicast flows (cells in the flow go to only one egress port), or multicast flows (in which case cells can go to many, even all, of the egress ports).

Data Sheet

PMC-2000164

ENHANCED TT1™ SWITCH FABRIC

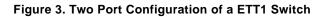

### 1.2.4 End-to-End Flow Control

The full queueing and flow control model is shown in Figure 4.

**NOTE:** Credits or backpressure are used at every transfer point to ensure that cells cannot be lost due to lack of buffer space.

## 1.2.5 TDM Service

The ETT1 TDM service provides guaranteed bandwidth and zero cell delay variation. These properties, which are not available from the best-effort service, mean that the TDM service might be used to provide an ATM CBR service, for example. The ETT1 core provides the TDM service at the same time as the best effort service, and TDM cells integrate smoothly with the flow of best-effort traffic. In effect, the TDM cells appear to the Scheduler to be cells of the highest precedence, even greater than level zero best-effort multicast traffic.

The TDM service operates by enabling a ETT1 port (and linecard) to reserve the crossbar fabric at some specified cell time in the future. The Scheduler is notified of this reservation and will not schedule any best-effort cells from the ingress port or to the egress port during that one cell time. Each port can make separate reservations according to whether it will send and/or receive a cell at each cell time.

Several egress ports may receive the same cell from a given ingress port; therefore, the TDM service is inherently a multicast service.

In order to provide a guaranteed bandwidth over a long period of time, an ingress port will want to repeat the reservations on a regular basis. To support this the ETT1 core uses an internal construct called a TDM

I

I

Data Sheet

PMC-2000164

ISSUE 3

PM9311/2/3/5 ETT1™ CHIP SET

ENHANCED TT1™ SWITCH FABRIC

Frame. A TDM Frame is simply a sequence of ingress and egress reservations. The length (number of cell times) of a TDM Frame is configurable up to a maximum of 1024 cells. The TDM Frame repeats after a certain fixed time. All ports are synchronized to the start of the TDM Frame, and operate cell-synchronously with respect to each other. Thus, at any cell time, every ETT1 port knows whether it has made a reservation to send or receive a TDM cell. See the application note "LCS-2 TDM Service in the ETT1 and TTX Switch Core", available from PMC-Sierra, Inc.

PMC-Sierra, Inc.

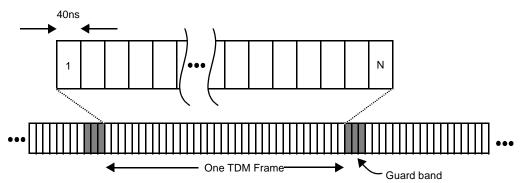

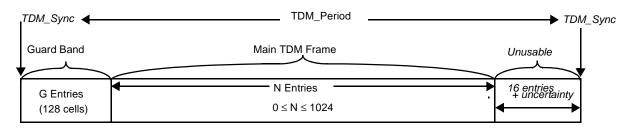

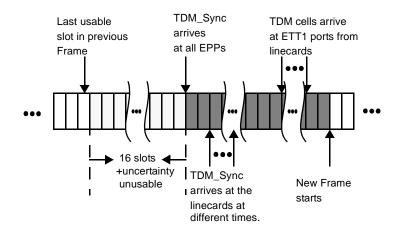

Figure 5 illustrates the idea of a TDM Frame. The TDM Frame has N slots (N is 1024 or less) where each slot is one 40ns cell time. The TDM Frame is repeated continuously, but adjacent TDM Frames are separated by a guard band of at least 144 cells.

Figure 5. The TDM Frame Concept

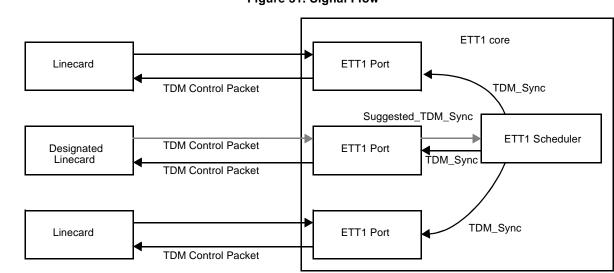

All of the ETT1 ports must be synchronized with respect to the start of the TDM Frame. This synchronization information is distributed via the Scheduler. The Scheduler can generate the synchronization pulses itself, or it can receive "Suggested Sync" pulses from a ETT1 port which can in turn receive synchronization signals from a linecard. The linecards do *not* need to be exactly synchronized to either the ETT1 core or the other linecards. The LCS protocol will compensate for the asynchrony between the linecard and the ETT1 core.

#### 1.2.6 Subport Mode (2.5 Gbit/s Linecards)

An ETT1 switch core can have up to 32 ports. Each port supports a linecard bandwidth in excess of 10 Gbit/s. This bandwidth might be used by a single linecard (for example, OC-192c), or the ETT1 port can be configured to share this bandwidth among up to four ports, each of 2.5 Gbit/s. This latter mode, specifically four 2.5 Gbit/s linecards, is referred to as subport mode, or sometimes as quad OC-48c mode.

A single ETT1 switch can have some ports in 'normal' mode, and some in subport mode; there is no restriction. The four levels of prioritized best-effort traffic are available in all configurations. However, there are some important differences between the two modes. One difference is that the LCS header must now identify the subport associated with each cell. Two bits in the LCS label fields are used for this purpose, as described below.

A second difference is that the EPP must carefully manage the output rate of each subport, so as not to overflow the buffers at the destination linecard, and this is also described below.

Data Sheet

PMC-2000164

I

ISSUE 3

ENHANCED TT1™ SWITCH FABRIC

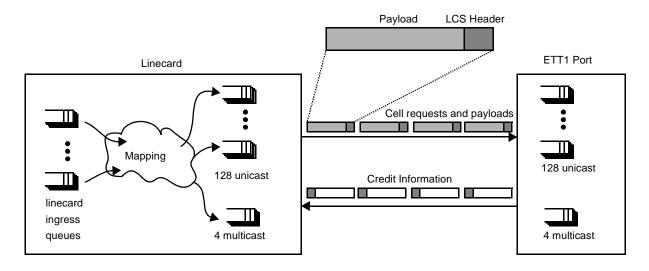

A third difference is that the EPP must maintain separate LCS request counters for each of the subports. It must also maintain separate egress queues. So the number of queues can increase four-fold in order to preserve the independence of each subport. Section 1.3 "Prioritized Best-Effort Queue Model" on page 30 describes the various queuing models in great detail.

#### 1.2.6.1 Identifying the Source Subport

The EPP manages a single physical stream of cells at 25M cells/second. In subport mode the EPP must look at each incoming cell and determine which subport has sent the cell. The LCS label field is used to achieve this. Two bits within the label (referred to in the LCS Specification as MUX bits) are used to denote the source subport, numbered 0 through 3. The MUX bits must be inserted in the LCS label before the cell arrives at the EPP. The MUX bits might be inserted at the source linecards themselves. Alternatively, they might be inserted by a four-to-one multiplexer device placed between the subport linecards and the EPP. In this latter case, the multiplexer device might not be able to re-calculate the LCS CRC. For maximum flexibility, the EPP can be configured to calculate the LCS CRC either with or without the MUX bits.

#### 1.2.6.2 Egress Cell Rate

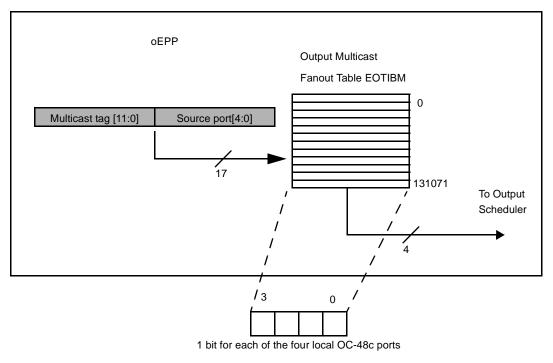

Within the EPP is an Output Scheduler process which is different from, and should not be confused with, the ETT1 Scheduler device. At every OC-192 cell time, the Output Scheduler looks at the egress queues and decides which cell should be forwarded to the attached egress linecard(s). In subport mode, the Output Scheduler will constrain the egress cell rate so as not to overflow any of the 2.5 Gbit/s links. It does this by operating in a strict round-robin mode, so that at any OC-192 cell time it will only try to send a cell for one of the subports. The four 2.5 Gbit/s subports are labeled as 0 through 3 ; at some cell time the Output Scheduler will only try to send a cell from the egress queues associated with subport 0. In the next time, it will only consider cells destined for subport 1, etc. If, at any cell time, there are no cells to be sent to the selected subport, then an Idle (empty) cell is sent. For example, if subports 0 and 3 are connected to linecards but subports 2 and 4 are disconnected, then the Output Scheduler will send a cell to 0, then an empty cell, then a cell to 3, then an empty cell, and then repeat the sequence. The effective cell rate transmitted to each subport will not exceed 6.25 M cells per second.